- CCD ທີ່ມີເຖິງ 16 cores, L2 cache ຂອງ 2 MB ຕໍ່ຫຼັກແລະ L3 cache ຂອງ 64 MB ຕໍ່ CCD, ມີ V-Cache ຂອງ 160 MB.

- ໂປເຊດເຊີ Desktop Ryzen ທີ່ມີເຖິງ 32 cores ແລະເຖິງ 448MB ຂອງ cache L3 ລວມຢູ່ໃນຕົວແປ X3D.

- Grimlock Point ແລະ Halo: ການຜະສົມຜະສານຂອງແກນ Zen 7/Zen 7c ແລະການປັບປຸງປະສິດທິພາບຕໍ່ວັດເຖິງ 36% ທີ່ 3W.

- TSMC A14 ເປັນ node ເປົ້າຫມາຍແລະປ່ອງຢ້ຽມຄາດຄະເນໄປສູ່ 2027-2028, ມີຄວາມເຂົ້າກັນໄດ້ AM5 ທີ່ເປັນໄປໄດ້.

ການຮົ່ວໄຫລຫລ້າສຸດຊີ້ໃຫ້ເຫັນ AMD Zen 7 (Grimlock) ເປັນບາດກ້າວອັນໃຫຍ່ຫຼວງຕໍ່ໄປຂອງບໍລິສັດ CPU ປະສິດທິພາບສູງຂໍ້ມູນສ່ວນໃຫຍ່ມາຈາກ ກົດMooາຍຂອງ Moore ຕາຍແລ້ວ ແລະ, ເຖິງແມ່ນວ່າພວກເຂົາເຫມາະສົມກັບການເຄື່ອນໄຫວ AMD ທີ່ຜ່ານມາ, ມັນດີທີ່ສຸດທີ່ຈະປິ່ນປົວພວກມັນດ້ວຍຄວາມລະມັດລະວັງຈົນກວ່າຈະມີການຢືນຢັນຢ່າງເປັນທາງການ..

ໃນບັນດາລັກສະນະທີ່ສໍາຄັນທີ່ຊ້ໍາກັນໃນຫຼາຍແຫຼ່ງແມ່ນການເພີ່ມຂຶ້ນໃນ cores ຕໍ່ chiplet, ໄດ້ double cache L2 ຕໍ່ core ແລະການກັບຄືນຂອງ 3D V-Cache ທີ່ມີຄວາມສາມາດຫຼາຍຂຶ້ນ. ສໍາລັບຜູ້ທີ່ປັບປຸງຢູ່ໃນສະເປນຫຼືເອີຣົບ, ໄດ້ ການສືບຕໍ່ທີ່ເປັນໄປໄດ້ຂອງ AM5 ມັນຈະເປັນການດີທີ່ຈະອັບເກຣດໂດຍທີ່ບໍ່ຕ້ອງປ່ຽນເມນບອດ.

ການຮົ່ວໄຫລເປີດເຜີຍຫຍັງກ່ຽວກັບ Zen 7 (Grimlock)?

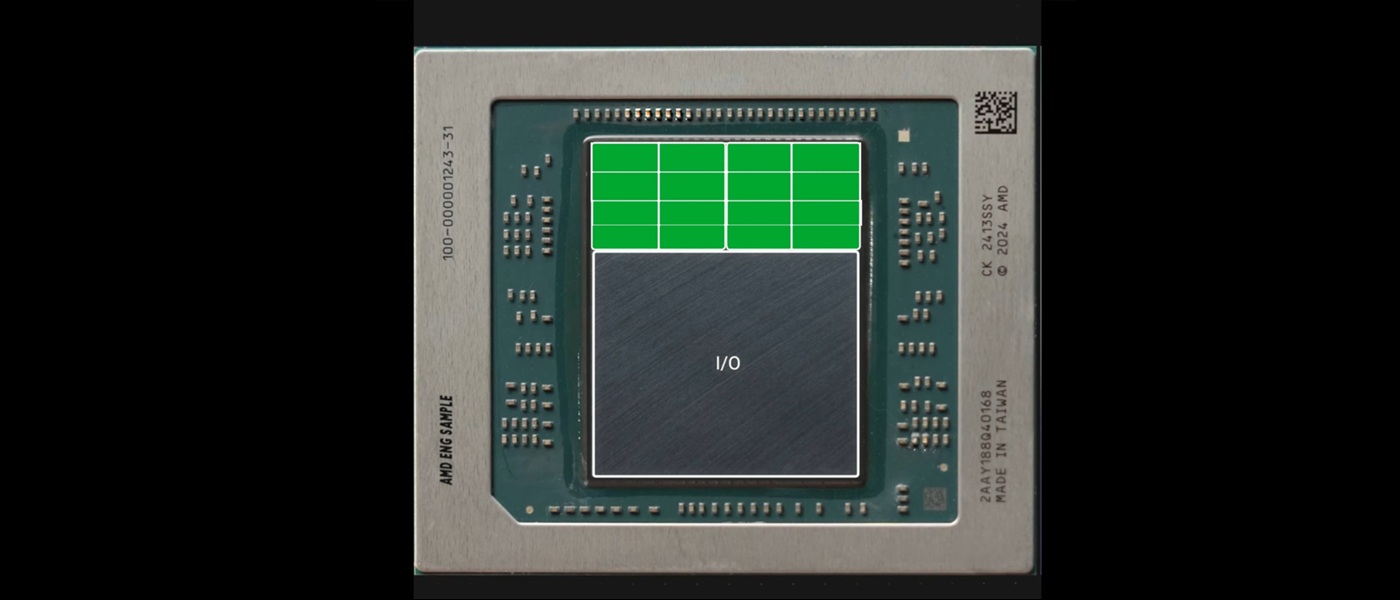

ຫົວໃຈຂອງຂ່າວລືແມ່ນຈະແຈ້ງ: ແຕ່ລະ Zen 7 CCD ຈະປະສົມປະສານເຖິງ 16 cores, ສອງເທົ່າຂອງການອອກແບບທີ່ຜ່ານມາທີ່ແນ່ນອນ, ກັບ 2 MB ຂອງ L2 cache ຕໍ່ຫຼັກ y 64 MB ຂອງ L3 ຕໍ່ chiplet. ວິທີການນີ້ເສີມສ້າງແບນວິດພາຍໃນແລະຄວາມໃກ້ຊິດຂອງຂໍ້ມູນ, ເສົາຫຼັກຂອງຍຸດທະສາດການເກັບຂໍ້ມູນຂອງ AMD.

ໃນຄອມພິວເຕີ desktop, ສອງ CCDs ຈະອະນຸຍາດໃຫ້ໂຮງງານຜະລິດຂອງ ສູງສຸດ 32 ແກນຕົວແປ X3D ຈະເພີ່ມເຖິງ 160 MB 3D V-Cache mosaic ຕໍ່ CCDຍົກສູງປະສິດທິພາບ L3 ຕໍ່ chiplet ກັບ 224 ເມກາໄບ ແລະ, ໃນສອງການຕັ້ງຄ່າ CCD, ເຖິງ 448 ເມກາໄບ ໂດຍລວມແລ້ວ.

Silverton ແລະ Silverking chiplets: ການແບ່ງສ່ວນແລະຖານຄວາມຈໍາ

ແຜນຂອບເຂດ Grimlock ຈະຖືກຈັດໃສ່ກັບ ສອງ chiplets CPU: Silverton ແລະ Silverking.

- Silverton ຈະເປັນຕົວແບບອັນດັບຕົ້ນໆ, ມີ 16 cores ແລະ 32 MB ຂອງ L2 cache. (2 MB ຕໍ່ຫຼັກ), 64 MB ຂອງ L3 cache ແລະສະຫນັບສະຫນູນສໍາລັບ 160 MB V-Cache ໂດຍ chiplet

- Silverking ຈະເລືອກ 8 cores, 16 MB ຂອງ L2 cache ແລະ 32 MB ຂອງ L3 cache, ໂດຍບໍ່ມີ 3D V-Cache..

ການສົມທົບສອງເຄື່ອງຈັກ Silverton ຈະເປີດປະຕູໄປສູ່ການຕັ້ງຄ່າຊັ້ນນໍາ 32 ແກນ ແລະ 64 ຫົວຂໍ້ເພີ່ມສອງເທົ່າ L2 ທັງຫມົດເປັນ 64 ເມກາໄບ ແລະການຕັ້ງຄ່າແຖບສໍາລັບ L3 cachet ໃນຕົວເລກທີ່ຈົນກ່ວາບໍ່ດົນມານີ້ເບິ່ງຄືວ່າສະເພາະກັບ ພາກສ່ວນມືອາຊີບ.

ຄາດຄະເນຜົນຜະລິດແລະ CPI

ຕົວເລກເບື້ອງຕົ້ນຊີ້ໃຫ້ເຫັນເຖິງການເພີ່ມຂຶ້ນ CPI ປະມານ 8% ເນື່ອງຈາກການອອກແບບໃຫມ່ cache, ກັບ ການປັບປຸງເພີ່ມເຕີມ 16-20% ໃນການເຮັດວຽກທີ່ບໍ່ແມ່ນເກມແລະການຂະຫຍາຍ multithreaded ທີ່ສໍາຄັນ. ໃນສະຖານະການ MT, ຫຼາຍແຫຼ່ງຊີ້ບອກ ເຖິງ 67% ເມື່ອທຽບກັບ Zen 6ສະຫນັບສະຫນູນໂດຍ CCD cores ຫຼາຍ, ການຄຸ້ມຄອງ cache ທີ່ດີກວ່າແລະຄວາມຫນາແຫນ້ນ.

ມັນບໍ່ແມ່ນທັງຫມົດກ່ຽວກັບການຕະຫຼາດ: ເນັ້ນຫນັກໃສ່ການ latency, bandwidth, ແລະການຈັດການສູງສຸດ. ໃນຄໍາສັບຕ່າງໆປະຕິບັດ, ນີ້ສາມາດແປໄດ້ ເວລາຕອບສະຫນອງຄວາມຫມັ້ນຄົງຫຼາຍ ໃນການສ້າງເນື້ອຫາ, ການລວບລວມ, ການຈໍາລອງ, ແລະການວິເຄາະ.

ມືຖື ແລະເຄື່ອງຫຼິ້ນແບບພົກພາ: Grimlock Point ແລະ Halo

ໃນການເຄື່ອນໄຫວ, APUs ຈຸດ Grimlock y Grimlock Halo ຈະປະສົມ nuclei Zen 7 ແລະ Zen 7c (ແລະ "ພະລັງງານຕ່ໍາ" ຕັນ), ເຮັດຊ້ໍາສູດຂອງລຸ້ນທີ່ຜ່ານມາ. ການຕັ້ງຄ່າກໍາລັງຖືກພິຈາລະນາສໍາລັບ 4 Zen 7 + 8 Zen 7c (ຈຸດ) ແລະ 8 Zen 7 + 12 Zen 7c (ຮາໂລ).

ປະສິດທິພາບຈະເປັນກຸນແຈ: ການປັບປຸງໃນ ປະສິດທິພາບຕໍ່ວັດ ເຖິງ ກ 36% ຢູ່ 3 W, 32% ຢູ່ 7 W, 25% ຢູ່ 12 W y 17% ຢູ່ 22 Wນີ້ຈະມີຜົນກະທົບໂດຍກົງຕໍ່ອຸປະກອນ ultralight ແລະ ມືຖື, ກັບ ຫຼຸດລົງເຟຣມຫນ້ອຍລົງ ແລະໂປຣໄຟລຄວາມຮ້ອນທີ່ສະດວກສະບາຍກວ່າ.

ການຜະລິດແລະການກໍານົດເວລາ

ສໍາລັບ CCDs, Zen 7 ຈະກໍານົດເປົ້າຫມາຍຂອງ node TSMC A14, ເປັນວິວັດທະນາການກ້າວຫນ້າທີ່ປ່ຽນແທນນາມສະກຸນ "2 nm" ຄລາສສິກ. ຄວາມສອດຄ່ອງຂອງອຸດສາຫະກໍາແນະນໍາການລົງຈອດທີ່, ຂຶ້ນກັບຜະລິດຕະພັນ, ມັນສາມາດຕັ້ງແຕ່ທ້າຍປີ 2027 ສໍາລັບມືຖືເຖິງ 2028 ສໍາລັບ desktop ແລະສູນຂໍ້ມູນ.

ຈັງຫວະນີ້ແມ່ນສອດຄ່ອງກັບ cadence ການປ່ອຍສອງປີແລະການເຕີບໂຕເຕັມທີ່ຂອງເສັ້ນຜ່າສູນກາງ, ບາງສິ່ງບາງຢ່າງທີ່ເຫັນໄດ້ຊັດເຈນໃນ ຄ່າໃຊ້ຈ່າຍໃນການຜະລິດ ແລະ ໃນ ຄວາມສັບສົນຂອງການລວມຫນ່ວຍຄວາມຈໍາທີ່ໃກ້ຊິດກັບຄອມພິວເຕີ້.

ເວທີ AI, ISA, ແລະຄຸນສົມບັດ

ແຫຼ່ງຂໍ້ມູນຈໍານວນຫນຶ່ງຊີ້ໃຫ້ເຫັນເຖິງຄວາມເປັນໄປໄດ້ ຄວາມເຂົ້າກັນໄດ້ຂອງ AM5ການຕັດສິນໃຈນີ້, ຖ້າໄດ້ຮັບການຢືນຢັນ, ຈະຊ່ວຍໃຫ້ການຮັບຮອງເອົາໃນຊ່ອງທາງການຂາຍຍ່ອຍຂອງເອີຣົບ. ໃນລະດັບຄໍາແນະນໍາ, ກ ຊຸດ ISA ໃໝ່ ດ້ວຍການສະຫນັບສະຫນູນດ້ານປະລິມານແລະການປັບປຸງໃນການກະກຽມຂໍ້ມູນສໍາລັບເຄື່ອງເລັ່ງ.

ຍິ່ງໄປກວ່ານັ້ນ, AMD ມີແລ້ວ ໄດ້ກ່າວເຖິງ Zen 7 ຢ່າງເປັນທາງການ ໃນແຜນທີ່ເສັ້ນທາງຂອງຕົນ, ຄາດວ່າຈະເປັນ ມໍເຕີມາຕຣິກເບື້ອງ ແລະຮູບແບບຂໍ້ມູນ AI ທີ່ກວ້າງຂວາງລວມເຂົ້າກັບຫຼັກ. ວິທີການໄປໄກກວ່າ AVX-512: ເປົ້າຫມາຍແມ່ນເພື່ອເລັ່ງການ inference ແລະກ່ອນ / ຫລັງການປຸງແຕ່ງພາຍໃນ. CPU ທົ່ວໄປ.

ເຊີບເວີແລະການປັບຂະຫນາດແບບມືອາຊີບ

ໃນພາກສະຫນາມ EPYC, ສະຖາປັດຕະຍະກໍາ Grimlock ຈະຊອກຫາ ການຂະຫຍາຍຕົວໃນຫຼັກແລະຖານຄວາມຈໍາ ຮັກສາປັດຊະຍາ chipletlatency ທີ່ສອດຄ່ອງແລະການເຂົ້າເຖິງ L3 ທີ່ກວ້າງຂວາງຈະຖືກຈັດລໍາດັບຄວາມສໍາຄັນ, ປັດໃຈສໍາຄັນສໍາລັບວຽກງານການວິເຄາະແລະຖານຂໍ້ມູນ. ສູນຂໍ້ມູນເອີຣົບ.

ເຖິງແມ່ນວ່າຕົວເລກທີ່ແນ່ນອນມີການປ່ຽນແປງຂຶ້ນຢູ່ກັບການກັ່ນຕອງ, ທິດທາງແມ່ນຈະແຈ້ງ: ຄວາມຫນາແຫນ້ນຫຼາຍຕໍ່ CCD, V-Cache ໃຫຍ່ກວ່າ ແລະປັບປຸງເສັ້ນທາງພາຍໃນເພື່ອສະຫນັບສະຫນູນການຈະລາຈອນຂໍ້ມູນແບບສຸມ.

ຖ້າແຜນການສອດຄ່ອງ, Zen 7 ຈະມາຮອດການລວມຕົວແບບ "cache-first" ຂອງ AMD: 16-core CCD, Duplicated L2, V-Cache ກ່ຽວກັບ steroids, ແລະການຊຸກຍູ້ຢ່າງຈະແຈ້ງໃນ AI ແລະປະສິດທິພາບສໍາລັບຜູ້ໃຊ້ໃນສະເປນແລະເອີຣົບ, hypothetical ໄດ້ ຄວາມຕໍ່ເນື່ອງ AM5 ແລະການສຸມໃສ່ການປະຕິບັດຕໍ່ວັດເຮັດໃຫ້ Grimlock ໃນ radar ສໍາລັບການຍົກລະດັບສົມເຫດສົມຜົນ, ໂດຍບໍ່ມີການ fanfare, ແຕ່ມີພື້ນຖານດ້ານວິຊາການຢ່າງຫຼວງຫຼາຍ.

ຂ້ອຍເປັນນັກເທັກໂນໂລຍີທີ່ກະຕືລືລົ້ນທີ່ໄດ້ຫັນຄວາມສົນໃຈ "geek" ຂອງລາວໄປສູ່ອາຊີບ. ຂ້າພະເຈົ້າໄດ້ໃຊ້ເວລາຫຼາຍກ່ວາ 10 ປີຂອງຊີວິດຂອງຂ້າພະເຈົ້າໂດຍການນໍາໃຊ້ເຕັກໂນໂລຊີທີ່ທັນສະໄຫມແລະ tinkering ກັບທຸກປະເພດຂອງໂຄງການອອກຈາກ curiosity ອັນບໍລິສຸດ. ຕອນນີ້ຂ້ອຍມີຄວາມຊ່ຽວຊານດ້ານເທັກໂນໂລຍີຄອມພິວເຕີ ແລະເກມວີດີໂອ. ນີ້ແມ່ນຍ້ອນວ່າຫຼາຍກວ່າ 5 ປີທີ່ຂ້ອຍໄດ້ຂຽນສໍາລັບເວັບໄຊທ໌ຕ່າງໆກ່ຽວກັບເຕັກໂນໂລຢີແລະວິດີໂອເກມ, ການສ້າງບົດຄວາມທີ່ຊອກຫາເພື່ອໃຫ້ທ່ານມີຂໍ້ມູນທີ່ທ່ານຕ້ອງການໃນພາສາທີ່ທຸກຄົນເຂົ້າໃຈໄດ້.

ຖ້າທ່ານມີຄໍາຖາມໃດໆ, ຄວາມຮູ້ຂອງຂ້ອຍແມ່ນມາຈາກທຸກສິ່ງທຸກຢ່າງທີ່ກ່ຽວຂ້ອງກັບລະບົບປະຕິບັດການ Windows ເຊັ່ນດຽວກັນກັບ Android ສໍາລັບໂທລະສັບມືຖື. ແລະຄໍາຫມັ້ນສັນຍາຂອງຂ້າພະເຈົ້າແມ່ນກັບທ່ານ, ຂ້າພະເຈົ້າສະເຫມີເຕັມໃຈທີ່ຈະໃຊ້ເວລາສອງສາມນາທີແລະຊ່ວຍທ່ານແກ້ໄຂຄໍາຖາມໃດໆທີ່ທ່ານອາດຈະມີຢູ່ໃນໂລກອິນເຕີເນັດນີ້.