- १६ कोर पर्यंत CCD, प्रति कोर २ MB L2 कॅशे आणि प्रति CCD ६४ MB L3 कॅशे, १६० MB V-कॅशेसह.

- X3D प्रकारांमध्ये 32 कोर पर्यंत आणि 448MB पर्यंत एकत्रित L3 कॅशे असलेले डेस्कटॉप रायझन प्रोसेसर.

- ग्रिमलॉक पॉइंट आणि हॅलो: झेन ७/झेन ७सी कोरचे मिश्रण आणि ३ वॅटवर ३६% पर्यंत प्रति वॅट कामगिरी सुधारणा.

- TSMC A14 हे लक्ष्य नोड म्हणून आणि २०२७-२०२८ पर्यंत अंदाजे विंडो, संभाव्य AM5 सुसंगततेसह.

नवीनतम लीक्स दर्शवितात की एएमडी झेन ७ (ग्रिमलॉक) कंपनीचे पुढील मोठे पाऊल म्हणून उच्च-कार्यक्षमता असलेला CPUबहुतेक डेटा येथून येतो मूरचा कायदा मृत झाला आहे आणि, जरी ते अलीकडील एएमडी हालचालींशी जुळतात, अधिकृत पुष्टी होईपर्यंत त्यांच्याशी सावधगिरी बाळगणे चांगले..

अनेक स्त्रोतांमध्ये पुनरावृत्ती झालेल्या प्रमुख वैशिष्ट्यांपैकी प्रत्येक चिपलेटमध्ये कोरमध्ये वाढ, प्रति कोर L2 कॅशे दुप्पट करा आणि 3D V-Cache परत करा जास्त क्षमतेसह. स्पेन किंवा युरोपमध्ये अपडेट करणाऱ्यांसाठी, AM5 ची संभाव्य सातत्य मदरबोर्ड न बदलता अपग्रेड करण्यासाठी हे एक संकेत असेल.

झेन ७ (ग्रिमलॉक) बद्दल लीकमधून काय उघड होते?

अफवेचे मूळ स्पष्ट आहे: प्रत्येक झेन ७ सीसीडीमध्ये १६ कोर समाविष्ट असतील., काही मागील डिझाइनच्या दुप्पट, सह प्रति कोर ४ एमबी एल३ y ६ एमबी एल२ प्रति चिपलेट. हा दृष्टिकोन अंतर्गत बँडविड्थ आणि डेटा प्रॉक्सिमिटीला बळकटी देतो, जे एएमडीच्या कॅशे स्ट्रॅटेजीचे आधारस्तंभ आहेत.

डेस्कटॉप संगणकांवर, दोन CCD प्रोसेसरना परवानगी देतील hasta 32 núcleos. रूपे X3D मध्ये प्रति CCD १६० MB पर्यंत 3D V-Cache मोज़ेक असेल.प्रति चिपलेट प्रभावी L3 वाढवणे ५०० एमबी आणि, दोन CCD कॉन्फिगरेशनमध्ये, पर्यंत ५०० एमबी एकूण.

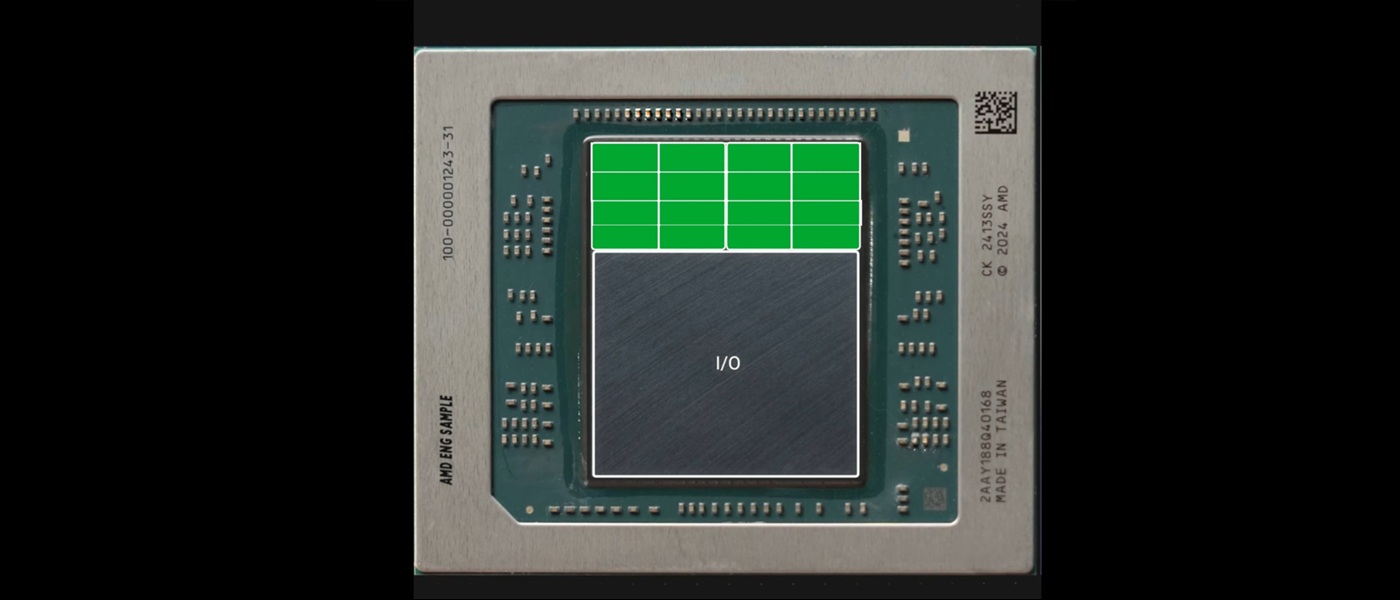

सिल्व्हरटन आणि सिल्व्हरकिंग चिपलेट्स: सेगमेंटेशन आणि कॅशिंग

ग्रिमलॉक रेंज प्लॅनची रचना अशी असेल की दोन CPU चिपलेट: सिल्व्हरटन आणि सिल्व्हरकिंग.

- सिल्व्हरटन हे टॉप-ऑफ-द-रेंज मॉडेल असेल, ज्यामध्ये १६ कोर आणि ३२ एमबी एल२ कॅशे असेल. (प्रति कोर २ एमबी), ६४ एमबी एल३ कॅशे आणि यासाठी समर्थन १६० एमबी व्ही-कॅशे चिपलेट द्वारे

- सिल्व्हरकिंग 3D V-कॅशेशिवाय 8 कोर, 16 MB L2 कॅशे आणि 32 MB L3 कॅशे निवडेल..

दोन सिल्व्हरटन इंजिन एकत्र केल्याने टॉप-ऑफ-द-लाइन कॉन्फिगरेशनचे दरवाजे उघडतील ८ कोर आणि १६ थ्रेडएकूण L2 दुप्पट करून ५०० एमबी आणि अलिकडेपर्यंत फक्त एकाच ठिकाणी वाटणाऱ्या आकृत्यांवर L3 कॅशेसाठी बार सेट करणे व्यावसायिक विभाग.

अंदाजे उत्पन्न आणि सीपीआय

प्राथमिक आकडेवारीत वाढ दिसून येते सीपीआय सुमारे ८% कॅशे रीडिझाइनमुळे, सह १६-२०% अतिरिक्त सुधारणा नॉन-गेमिंग वर्कलोड्स आणि लक्षणीय मल्टीथ्रेडेड स्केलिंगमध्ये. एमटी परिस्थितींमध्ये, अनेक स्त्रोत सूचित करतात झेन ६ च्या तुलनेत ६७% पर्यंतअधिक CCD कोर, चांगले कॅशे व्यवस्थापन आणि घनता द्वारे समर्थित.

हे सर्व मार्केटिंगबद्दल नाही: येथे लेटन्सी, बँडविड्थ आणि पीक हँडलिंगवर भर दिला जातो. व्यावहारिक भाषेत, याचा अर्थ असा होऊ शकतो की अधिक स्थिर प्रतिसाद वेळा सामग्री निर्मिती, संकलन, सिम्युलेशन आणि विश्लेषणात.

हँडहेल्ड आणि पोर्टेबल कन्सोल: ग्रिमलॉक पॉइंट आणि हॅलो

गतिशीलतेमध्ये, APUs ग्रिमलॉक पॉइंट y ग्रिमलॉक हॅलो केंद्रके मिसळतील झेन ७ आणि झेन ७सी (आणि "लो-पॉवर" ब्लॉक), अलिकडच्या पिढ्यांच्या सूत्राची पुनरावृत्ती. यासाठी कॉन्फिगरेशनचा विचार केला जात आहे ४ झेन ७ + ८ झेन ७सी (बिंदू) आणि ४ झेन ७ + ८ झेन ७सी (नमस्कार).

कार्यक्षमता महत्त्वाची असेल: सुधारणा प्रति वॅट कामगिरी पर्यंत ३ वॅट्सवर ३६%, ३ वॅट्सवर ३६%, ३ वॅट्सवर ३६% y ३ वॅट्सवर ३६%याचा थेट परिणाम अल्ट्रालाईट उपकरणांवर होईल आणि हँडहेल्ड, सह कमी फ्रेम ड्रॉप्स आणि अधिक आरामदायी थर्मल प्रोफाइल.

उत्पादन आणि वेळापत्रक

CCD साठी, Zen 7 नोडला लक्ष्य करेल टीएसएमसी ए१४, एक प्रगत उत्क्रांती जी क्लासिक "2 nm" नामकरणाची जागा घेते. औद्योगिक फिट असे लँडिंग सूचित करते जे उत्पादनावर अवलंबून, ते मोबाईलसाठी २०२७ च्या अखेरीपासून ते डेस्कटॉप आणि डेटा सेंटरसाठी २०२८ पर्यंत असू शकते..

ही गती द्वैवार्षिक रिलीज कॅडेन्स आणि अत्याधुनिक नोड्सच्या परिपक्वतेशी सुसंगत आहे, जी या क्षेत्रात देखील लक्षणीय आहे. उत्पादन खर्च आणि मध्ये संगणकाच्या जवळ अधिक मेमरी एकत्रित करण्याची जटिलता.

एआय प्लॅटफॉर्म, आयएसए आणि वैशिष्ट्ये

अनेक स्रोत संभाव्यतेकडे निर्देश करतात AM5 सुसंगतताजर हा निर्णय पुष्टी झाला तर युरोपियन रिटेल चॅनेलमध्ये दत्तक घेण्यास मदत होईल. सूचना स्तरावर, अ नवीन आयएसए संच एक्सीलरेटर्ससाठी क्वांटायझेशन सपोर्ट आणि डेटा तयारीमध्ये सुधारणांसह.

शिवाय, एएमडीने आधीच अधिकृतपणे झेन ७ चा उल्लेख केला आहे त्याच्या रोडमॅपमध्ये, अपेक्षा करत आहे की मॅट्रिक्स मोटर आणि कोरमध्ये एकत्रित केलेले विस्तृत एआय डेटा फॉरमॅट. हा दृष्टिकोन AVX-512 च्या पलीकडे जातो: ध्येय म्हणजे अनुमान आणि पूर्व/उत्तर-प्रक्रिया गतिमान करणे. जनरलिस्ट सीपीयू.

सर्व्हर आणि व्यावसायिक स्केलिंग

EPYC क्षेत्रात, ग्रिमलॉक आर्किटेक्चर शोधेल कोर आणि कॅशेमध्ये स्केलिंग चिपलेट तत्वज्ञान राखणेविश्लेषणात्मक आणि डेटाबेस वर्कलोडसाठी महत्त्वाचे घटक, सातत्यपूर्ण विलंब आणि विस्तृत L3 प्रवेश यांना प्राधान्य दिले जाईल. युरोपियन डेटा सेंटर्स.

जरी गाळण्याच्या पद्धतीनुसार अचूक संख्या बदलत असली तरी, दिशा स्पष्ट आहे: प्रति CCD अधिक घनता, मोठा व्ही-कॅशे आणि सघन डेटा ट्रॅफिकला समर्थन देण्यासाठी अंतर्गत मार्ग सुधारित केले.

जर योजना जुळल्या तर, एएमडीच्या "कॅशे-फर्स्ट" मॉडेलला एकत्रित करून झेन ७ येईल: १६-कोर सीसीडी, डुप्लिकेट L2, स्टिरॉइड्सवर V-कॅशे, आणि AI आणि कार्यक्षमतेत स्पष्ट वाढस्पेन आणि युरोपमधील वापरकर्त्यांसाठी, काल्पनिक AM5 सातत्य आणि प्रति वॅट कामगिरीवर लक्ष केंद्रित केल्याने ग्रिमलॉकला वाजवी अपग्रेडसाठी रडारवर आणले जाते, तेही धाडस न करता, परंतु मोठ्या तांत्रिक पायासह.

मी एक तंत्रज्ञान उत्साही आहे ज्याने त्याच्या "गीक" आवडींना व्यवसायात बदलले आहे. मी माझ्या आयुष्यातील 10 वर्षांहून अधिक काळ अत्याधुनिक तंत्रज्ञानाचा वापर करून आणि सर्व प्रकारच्या कार्यक्रमांना निव्वळ उत्सुकतेपोटी घालवले आहे. आता मी कॉम्प्युटर टेक्नॉलॉजी आणि व्हिडिओ गेम्समध्ये स्पेशलायझेशन केले आहे. याचे कारण असे की, मी 5 वर्षांहून अधिक काळ तंत्रज्ञान आणि व्हिडिओ गेमवरील विविध वेबसाइट्ससाठी लिहित आहे, प्रत्येकाला समजेल अशा भाषेत तुम्हाला आवश्यक असलेली माहिती देण्यासाठी लेख तयार करत आहे.

तुम्हाला काही प्रश्न असल्यास, माझे ज्ञान विंडोज ऑपरेटिंग सिस्टीम तसेच मोबाइल फोनसाठी अँड्रॉइडशी संबंधित सर्व गोष्टींपासून आहे. आणि माझी वचनबद्धता तुमच्याशी आहे, मी नेहमी काही मिनिटे घालवण्यास तयार आहे आणि या इंटरनेटच्या जगात तुम्हाला पडणाऱ्या कोणत्याही प्रश्नांचे निराकरण करण्यात मदत करण्यास तयार आहे.