- सी-स्टेट्स निष्क्रिय असताना बचत करतात (खोल = अधिक विलंब), पी-स्टेट्स लोड अंतर्गत वारंवारता/व्होल्टेज समायोजित करतात.

- दोन्ही ऑर्थोगोनल आहेत: उच्च वारंवारतेवर चालल्यानंतर CPU गाढ झोपू शकते.

- C6/C7 विलंब गेमिंग, ऑडिओ आणि नेटवर्किंगवर परिणाम करतात; लोडवर आधारित कमाल C-स्टेट समायोजित करा.

- स्थिरता न गमावता मोजण्यासाठी आणि नियंत्रित करण्यासाठी साधने (विंडोज आणि लिनक्स) आणि BIOS/OS प्रोफाइल वापरा.

आधुनिक प्रोसेसरमध्ये, पॉवर मॅनेजमेंट हे एकच स्विच नसून एक संच आहे समन्वित यंत्रणा (CPU च्या C-स्टेट्स आणि P-स्टेट्स, इतरांसह) ज्याचा वापर ऑपरेटिंग सिस्टम, फर्मवेअर आणि सीपीयू स्वतः रिअल टाइममध्ये वीज वापर, तापमान आणि कार्यप्रदर्शन समायोजित करण्यासाठी करतात. हा लेख संक्षिप्त शब्दांचा तो गोंधळ काढून टाकतो आणि व्यवस्थित करतो जेणेकरून तुमचा संगणक वीज वाचवतो किंवा वेग वाढवतो तेव्हा काय घडत आहे हे तुम्हाला समजू शकेल.

जरी प्रत्येक उत्पादक आणि CPU कुटुंब स्वतःचा स्पर्श जोडते, तरी पाया सामान्य आहे: ACPI मानक "अवस्था" परिभाषित करते सिस्टम, डिव्हाइसेस आणि प्रोसेसरसाठी. येथे तुम्हाला C-स्टेट्स आणि P-स्टेट्समधील फरक, ते G/S/D-स्टेट्सशी कसे संबंधित आहेत, त्यांचा लेटन्सीवर वास्तविक जगात काय परिणाम होतो, गेमर्स आणि व्यावसायिक ऑडिओफाइल्स अनेकदा गाढ झोप का बंद करतात आणि विंडोज, लिनक्स आणि ESXi सारख्या वातावरणात वापरण्यासाठी कोणती व्यावहारिक साधने उपलब्ध आहेत ते दिसेल.

थोडक्यात ACPI

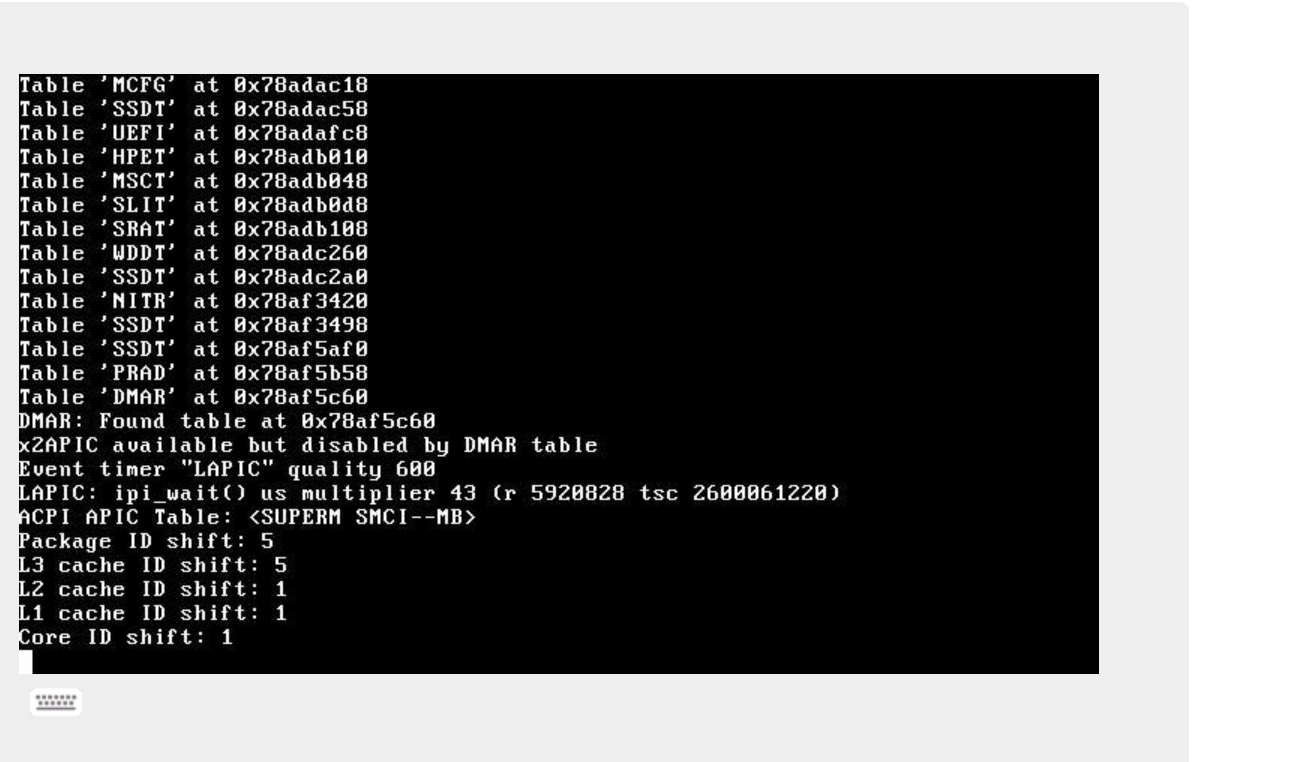

एसीपीआय (प्रगत कॉन्फिगरेशन आणि पॉवर इंटरफेस) हे पीसी आणि सर्व्हरमध्ये पॉवर ऑर्केस्ट्रेट करणारे मानक आहे आणि ते APM ची जागा अधिक नियंत्रण आणि ग्रॅन्युलॅरिटीने घेतली. ९० च्या दशकात इंटेल, मायक्रोसॉफ्ट आणि तोशिबाच्या हातून त्याचा जन्म झाला आणि त्यात ६४-बिट, मल्टीप्रोसेसिंग, आधुनिक बसेस (PCIe, SATA, USB 3.x) आणि इव्हेंट डिटेक्शन (उदा. पॉवर बटण) यांचा समावेश झाला.

जरी ACPI प्रामुख्याने x86 कुटुंबात वापरले जात असले तरी, ते इतर आर्किटेक्चर्सवर देखील तैनात केले गेले आहे. तथापि, ARM मोबाईल डिव्हाइसेसवर, मालकी धोरणे वापरली जातात (जसे की मोठे. लहान आणि विषम क्लस्टर्स) भारानुसार कार्यक्षमता आणि प्रतिसाद संतुलित करणे.

जागतिक आणि निलंबित राज्ये (जी-राज्ये आणि एस-राज्ये)

जागतिक राज्ये प्रणालीच्या संपूर्ण स्थितीचे वर्णन करतात. सर्वात महत्वाचे म्हणजे G0/S0 (कार्यरत), जिथे संगणक सक्रिय आहे. अलीकडील हार्डवेअरवर आहे S0 (S0 चे उपसंच) जे SoC स्लीपिंगच्या काही भागासह अतिशय उत्तम स्लीप मोड्ससाठी परवानगी देतात, विशेषतः लॅपटॉपमध्ये.

- G0/S0: सिस्टम कार्यरत आहे.

- G1 (झोपलेला): S1, S2, S3 (RAM वर निलंबित) आणि S4 (डिस्कवर हायबरनेट) कव्हर करते. S3 रॅमला चालना देतो. जलद पुन्हा सुरू करण्यासाठी; S4 मेमरी नॉन-व्होलॅटाइल स्टोरेजमध्ये फ्लश करते.

- G2/S5 (सॉफ्ट-ऑफ): कार्यक्रमांद्वारे (कीबोर्ड, नेटवर्क, इ.) जागे होण्यास अनुमती देण्यासाठी किमान पॉवरसह तार्किक शटडाउन.

- G3 (मेकॅनिकल-ऑफ): प्रत्यक्ष बंद; प्रति बॅटरी फक्त RTC टिकते.

लक्षात ठेवा की प्रोसेसरचे सी-स्टेट्स G0/S0 मध्ये राहतात.: जेव्हा सिस्टम G1 मध्ये प्रवेश करते, तेव्हा CPU पॅकेज बंद होते आणि C-स्टेट्स प्ले होणे थांबवतात.

डिव्हाइस स्टेटस (डी-स्टेट्स)

ACPI हे पेरिफेरल्स कसे झोपतात किंवा जागे होतात हे देखील परिभाषित करते. D0 हे "पूर्ण ऑपरेशन" च्या समतुल्य आहे, D1/D2 हे मध्यवर्ती आहेत (डिव्हाइस-अवलंबित) आणि D3 हॉट (सहायक शक्तीसह, बसला प्रतिसाद देणारे) किंवा कोल्ड (पूर्णपणे बंद, प्रतिसाद न देणारे) मध्ये विभागले जातात. उदाहरणार्थ, इतर डिव्हाइसेस झोपेत असताना नेटवर्क कार्ड संगणकाला जागृत करण्यास अनुमती देते.

टी-स्टेट्स: घड्याळाचे मॉड्युलेशन, शेवटचा उपाय

P आणि C व्यतिरिक्त, आहे घड्याळ मॉड्युलेशन (टी-स्टेट्स): एक प्रकारचा PWM जो अंतर्गत घड्याळाच्या स्पंदना एका पॅटर्नमध्ये दाबतो (उदा., प्रत्येक 8 पैकी 1), जाहिरात केलेली बेस फ्रिक्वेन्सी न बदलता क्रियाकलाप कमी करतो. हे थर्मल किंवा आपत्कालीन प्रतिमेजर (PROCHOT) म्हणून आहे आणि IA32_CLOCK_MODULATION द्वारे नियंत्रित केले जाते, ज्यामध्ये MSR_*_PERF_LIMIT_REASONS मध्ये कारणे/लॉग असतात.

जरी काही कागदपत्रे ते "अप्रासंगिक" मानतात, प्रत्यक्षात ते लॅपटॉपवर चांगल्या थर्मल डिझाइनसह दिसत राहते. आणि सततच्या भारांखाली. जर तुम्हाला विंडोज किमान EIST पेक्षा कमी "वेग" नोंदवत असल्याचे दिसले, तर कदाचित T-स्टेट सक्रिय (क्लॉक गेटिंग) असेल.

एम-स्टेट्स: मेमरी सेव्हिंग्ज

सिस्टम निष्क्रिय असताना DRAM सबसिस्टम पॉवर वापर कमी करण्यासाठी ACPI मेमरी स्टेट्स देखील प्रदान करते. M0 हे सामान्य ऑपरेशन आहे.M1/M2 आणि इतर मोड्स मेमरीला स्वतः रिफ्रेश करण्यास भाग पाडतात आणि वेळेचा वेग कमी करतात, ज्यामुळे जास्त वेळ जागृत राहण्याच्या विलंबांसह पॉवर कमी होते. हे वापरकर्त्याला कमी दृश्यमान असतात, परंतु एकूण बचतीत योगदान देतात.

प्रोसेसर सी-स्टेट्स: डोके ठेवून झोपा

आता लेखाच्या विषयावर चर्चा करूया: सी-स्टेट्स आणि पी-स्टेट्स. सी-स्टेट्स म्हणजे कर्नल किंवा पॅकेजच्या निष्क्रिय अवस्था. संख्या जितकी जास्त तितकी झोप जास्त खोल आणि जास्त बचत, पण जास्त वेक-अप लेटन्सी देखील. त्यांना HLT किंवा MWAIT सारख्या विशेषाधिकारित सूचनांसह विनंती केली जाते (नंतरचे स्पष्टपणे Cx आणि सबस्टेटसची विनंती करू शकते), आणि क्षमता मॅपिंग ACPI (_CST) द्वारे OS पर्यंत पोहोचते.

- C0: सामान्य अंमलबजावणी. इथेच P-स्टेट्स भूमिका बजावतात.

- C1/C1E (थांबवा): गाभा थांबतो, जवळजवळ त्वरित परतावा C0 पर्यंत; C1E वापर आणखी कमी करते.

- C2 (थांबवा-घड्याळ): घड्याळाचे सिग्नल थांबले आहेत, परत येण्यास थोडा जास्त वेळ लागतो.

- C3 (झोप/गाढ झोप): L1/L2 शेवटच्या कॅशे (LLC) वर फ्लश केले जाते आणि कोर घड्याळे बंद केली जातात; केवळ केंद्रकाची आवश्यक स्थिती जतन केली जाते..

- C6 आणि त्यावरील: कोर बंद करता येतो आणि त्याचा संदर्भ समर्पित SRAM मध्ये जतन करता येतो, ज्यामुळे कोर व्होल्टेज ~0 V पर्यंत खाली येतो; बाहेर पडल्यावर, कोर स्थिती पुनर्संचयित केली जाते. काही मॉडेल्स अलीकडील प्लॅटफॉर्मवर C10 पर्यंत एक्सपोज करतात.

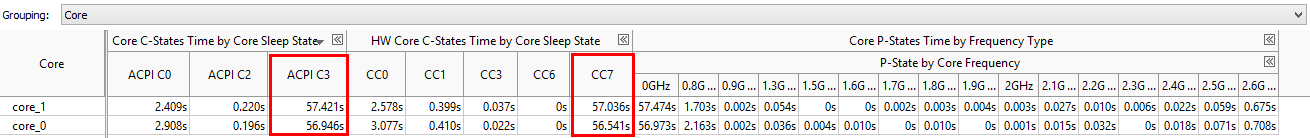

प्रति केंद्रक C-अवस्था (CC-अवस्था) व्यतिरिक्त, चे समतल आहे पॅकेज सी-स्टेट्स (पीसी-स्टेट्स) जे सर्व कोर परवानगी देतात तेव्हा शेअर्ड ब्लॉक्स (LLC सारखे) बंद करतात. अवैध संयोजने आहेत (जर कोर C0 मध्ये असेल तर पॅकेट PC6 मध्ये असू शकत नाही), आणि CPU लक्ष्य विलंब आणि रेसिडेन्सीजवर आधारित टियरला स्वयंचलितपणे "प्रमोट" किंवा "डिमोट" करू शकते.

विलंब महत्त्वाचा: C1 फक्त काही डझन चक्रांमध्ये सोडले जाते., तर C6/C7 ला शेकडो मायक्रोसेकंद खर्च येऊ शकतात. म्हणूनच, प्रोसेसर वारंवार गाढ झोपेत गेल्यास विलंब-संवेदनशील भार (गेमिंग, रिअल-टाइम ऑडिओ, डिमांडिंग नेटवर्किंग) प्रभावित होतात.

कामगिरी पी-स्टेट्स: वारंवारता आणि व्होल्टेज

सी-स्टेट्स "जेव्हा कोणतेही काम नसते तेव्हा झोपतात", तर पी-स्टेट्स "जेव्हा वेग समायोजित करतात" हो, काम आहे, पण त्यासाठी जास्तीत जास्त प्रयत्न करावे लागत नाहीत.". P0 ही सर्वोच्च कामगिरीची स्थिती (सर्वोच्च वारंवारता/व्होल्टेज) आहे, त्यानंतर P1, P2… प्रत्येकी कमी होत जाणाऱ्या वारंवारता-व्होल्टेज जोड्यांसह येतात. हे टेबल ACPI (_PSS) द्वारे OS ला घोषित केले जातात आणि IA32_PERF_CTL/IA32_PERF_STATUS सारख्या MSR द्वारे नियंत्रित केले जातात.

ऐतिहासिकदृष्ट्या ऑपरेटिंग सिस्टमने पी-स्टेट्सची आवश्यकता होती (इंटेलवर EIST/स्पीडस्टेप, AMD वर PowerNow!), परंतु आज ते सामान्य आहे हार्डवेअर-नियंत्रित कामगिरी स्थिती (HWP/स्पीड शिफ्ट): ऑपरेटिंग सिस्टम प्राधान्य (कार्यप्रदर्शन/बचत) दर्शवते आणि CPU मिलिसेकंदांमध्ये अचूक बिंदू ठरवते, अगदी बारीक प्रति-कोर ग्रॅन्युलॅरिटीसह.

एक महत्त्वाचा तपशील: पी-स्टेट्स आणि सी-स्टेट्स "ऑर्थोगोनल" आहेत.तुम्ही P0 (उच्च वारंवारता) वर असू शकता आणि निष्क्रिय झाल्यावर, C6 प्रविष्ट करू शकता. उलट, P2 वर सतत लोड अंतर्गत, कोर कार्यान्वित होत असल्याने C-स्टेट्स नसतात (C0). म्हणूनच "फ्रिक्वेन्सी/व्होल्टेज" (P) ला "निष्क्रिय" (C) पासून मानसिकरित्या वेगळे करणे ही चांगली कल्पना आहे.

APM ते ACPI पर्यंत: एक आदर्श बदल

APM हे पूर्वीचे API होते जे प्रामुख्याने BIOS आणि ड्रायव्हर्समधून व्यवस्थापित केले जात असे. ते परवानगी देते निष्क्रिय पेरिफेरल्स बंद करा आणि साध्या जागतिक स्थिती परिभाषित करा., परंतु सुरक्षेच्या कारणास्तव CPU हे OS च्या थेट नियंत्रणाबाहेर होते. ACPI हे एका समृद्ध, अधिक प्रमाणित मॉडेलमध्ये विकसित झाले, ज्यामध्ये टेबल वर्णने, बारीक नियंत्रण आणि फर्मवेअर, OS आणि हार्डवेअरमधील जवळचे सहकार्य होते.

सी-स्टेट्समध्ये कसे प्रवेश करायचे आणि कसे बाहेर पडायचे

जेव्हा शेड्युलरकडे कोणतेही थ्रेड तयार नसतात, तेव्हा ते लक्ष्य C-स्टेटच्या संकेतासह HLT किंवा MWAIT कार्यान्वित करते; व्यत्यय झोप "भंग" करतात आणि कोर C0 वर परत करा. खाजगी कॅशे C3 वर फ्लश केले जातात; संदर्भ C6 वर SRAM मध्ये जतन केला जातो आणि व्होल्टेज शून्यावर कमी केला जातो. काही CPU पॉवर अवेअर इंटरप्ट राउटिंग (PAIR) लागू करतात जेणेकरून इंटरप्ट्सना रूट केले जाऊ शकेल आधीच सक्रिय कोर (जतन करण्यासाठी) किंवा निष्क्रिय कोरसाठी (कामगिरीसाठी), योग्यतेनुसार.

टर्बो, टीडीपी आणि पॉवर मर्यादा

प्रोसेसर टीडीपीची व्याख्या करतात की कूलिंग सिस्टम सतत विरघळण्यास सक्षम असावी (PL1: सुरक्षित सरासरी पॉवर). वर, जास्त पॉवर असलेल्या खिडक्या आत जाऊ शकतात (पीएल२, आणि प्लॅटफॉर्मवर अवलंबून PL3/PL4 सारखे अतिरिक्त स्तर) मर्यादित कालावधीसाठी. जर थर्मल आणि इलेक्ट्रिकल हेडरूम असेल, तर कोर टर्बोद्वारे बेस फ्रिक्वेन्सी ओलांडू शकतो, अगदी असममित आकार (कमी सक्रिय कोरसह अधिक टर्बो).

जेव्हा तापमान मर्यादेपेक्षा जास्त होते किंवा VRM/शक्तीची मागणी असते, प्रोचॉट सक्रिय केले जाऊ शकते आणि चिप संरक्षित करण्यासाठी टी-स्टेट किंवा फ्रिक्वेन्सी क्लिपिंग प्रविष्ट करा. पातळ लॅपटॉपमध्ये हे वर्तन सामान्य आहे.

विंडोज: पॉवर प्लॅन, रीडिंग्ज आणि काउंटर

विंडोज ऑफर "ऊर्जा बचत" सारख्या योजना, “संतुलित” आणि “उच्च कार्यक्षमता”. पहिले कल पी-स्टेट्स आक्रमकपणे कमी करा आणि शांत झोप घ्यातिसरा उच्च फ्रिक्वेन्सी राखतो आणि कार्यक्षमतेच्या खर्चावर विलंब कमी होण्यापासून रोखतो. "संतुलित" मध्यम मार्ग शोधण्याचा प्रयत्न करतो.

टास्क मॅनेजरमध्ये, "वेग" हे एक कृत्रिम मेट्रिक आहे जे प्रति कोर सरासरी आणि मॉड्युलेशन ड्यूटी विचारात घेते जर टी-स्टेट्स असतील तर. ते बेस (टर्बो) पेक्षा जास्त असू शकते किंवा किमान EIST (गेटिंग) पेक्षा कमी असू शकते. प्रगत टेलीमेट्रीसाठी, “\प्रोसेसर माहिती(_एकूण)\% प्रोसेसर कामगिरी” काउंटर CPU द्वारे प्रभावी कामगिरीची टक्केवारी दर्शवते.

निदान करण्यासाठी किंवा समायोजित करण्यासाठी उपयुक्तता आहेत: सीपीयू-झेड (मूलभूत डेटा), एचडब्ल्यूआयएनएफओ (सेन्सर्स), थ्रॉटलस्टॉप (घड्याळे, प्रति कोर सी-स्टेट्स आणि प्रोचोट/मॉड्युलेशन नियंत्रण), किंवा पार्ककंट्रोल (कोअर पार्किंग ट्यूनिंग/सी-स्टेट्स) जे लपलेल्या पॉवर प्लॅन पॅरामीटर्सना स्पर्श करतात (powercfg "IDLE_PROMOTE/DEMOTE" इत्यादी संपादित करण्यास अनुमती देते).

लिनक्स: सीपीयूपॉवर, टर्बोस्टॅट आणि कोअरफ्रेक

लिनक्समध्ये, अशी साधने सीपीयू पॉवर गव्हर्नर, फ्रिक्वेन्सी रेंज आणि ट्रांझिशन लेटेन्सीज दाखवा; टर्बोस्टॅट सी-स्टेटनुसार MSR, कोर परफॉर्म लिमिट कारणे (MSR_CORE_PERF_LIMIT_REASONS) आणि रेसिडेन्सीज प्रदर्शित करते; आणि कोरफ्रीक प्रत्येक कोर/पॅकेजसाठी परिपूर्ण फ्रिक्वेन्सी, सी-स्टेट्स आणि टर्बोचे तपशीलवार दृश्य प्रदान करते.

एक व्यावहारिक बारकावे: काही संगणकांवर, ड्रायव्हर intel_idle BIOS निर्बंधांकडे दुर्लक्ष करू शकते. C-स्टेट्सवर आणि त्यांचे स्वतःचे टेबल वापरतात. इतरांमध्ये, फर्मवेअर MSR द्वारे OS साठी परवानगी असलेल्या सर्वात खोल C-स्टेटला "लॉक" करते.

BIOS/UEFI आणि प्रोफाइल: खरोखर कोण जबाबदार आहे?

BIOS/UEFI सेटिंग्जमध्ये ते सहसा दिसतात की स्विचेस: EIST/स्पीडस्टेप, टर्बोबूस्ट आणि CPU C-स्टेट्सयाव्यतिरिक्त, बरेच सर्व्हर तुम्हाला पॉवर प्रोफाइल निवडण्याची परवानगी देतात: "कमाल कामगिरी" (कमीतकमी विलंबांसह सर्वकाही सर्वोत्तम) किंवा "OS नियंत्रित/कस्टम," जिथे हायपरवाइजर किंवा OS P/C-स्टेट्स नियंत्रित करते. "OS नियंत्रण मोड" निवडल्याने बुद्धिमत्ता ऑपरेटिंग सिस्टमला सोपवते.

जर तुम्ही ESXi सारखे हायपरवाइजर वापरत असाल, तर ते एकत्र करणे चांगली कल्पना आहे "उच्च कार्यक्षमता" योजनेसह BIOS मध्ये OS नियंत्रण मोड जेव्हा कामगिरी कमी करणे हे ध्येय असते तेव्हा हायपरवाइजरचा (उदाहरणार्थ NSX-T, एज नोड्स किंवा लेटन्सी-सेन्सिटिव्ह फंक्शन्ससह). त्या परिस्थितीत, तुम्हाला P-स्टेट 0 अधिक वारंवार दिसेल आणि C-स्टेट C0/C1 पर्यंत मर्यादित असतील; "संतुलित" योजनेसह, होस्ट कमी P-स्टेट आणि खोल C-स्टेटवर अधिक अवलंबून असेल.

या संपूर्ण सी-स्टेट्स आणि पी-स्टेट्स गोंधळाचा सारांश असा आहे: एसीपीआय फ्रेम परिभाषित करते, सी-स्टेट्स काम नसताना वीज वाचवतात, पी-स्टेट्स लोड अंतर्गत उच्च/कमी गियर समायोजित करतात, टी-स्टेट्स अति उष्णतेमध्ये दिवस वाचवतात आणि एम-स्टेट्स मेमरी वॅट्स कमी करतात. तुमच्या वापरासाठी योग्य प्रोफाइल निवडणे ही गुरुकिल्ली आहे., योग्य साधनांनी मोजमाप करा आणि आवश्यक असल्यास, विश्रांतीच्या खोलीवर योग्य मर्यादा सेट करा.

विविध डिजिटल माध्यमांमध्ये दहा वर्षांहून अधिक अनुभव असलेले संपादक तंत्रज्ञान आणि इंटरनेट समस्यांमध्ये विशेषज्ञ आहेत. मी ई-कॉमर्स, कम्युनिकेशन, ऑनलाइन मार्केटिंग आणि जाहिरात कंपन्यांसाठी संपादक आणि सामग्री निर्माता म्हणून काम केले आहे. मी अर्थशास्त्र, वित्त आणि इतर क्षेत्रातील वेबसाइट्सवर देखील लिहिले आहे. माझे काम देखील माझी आवड आहे. आता, मधील माझ्या लेखांद्वारे Tecnobits, मी सर्व बातम्या आणि नवीन संधी एक्सप्लोर करण्याचा प्रयत्न करतो ज्या तंत्रज्ञानाचे जग आम्हाला आमचे जीवन सुधारण्यासाठी दररोज ऑफर करते.