- 16 ਕੋਰ ਤੱਕ ਦੇ CCD, ਪ੍ਰਤੀ ਕੋਰ 2 MB ਦਾ L2 ਕੈਸ਼ ਅਤੇ ਪ੍ਰਤੀ CCD 64 MB ਦਾ L3 ਕੈਸ਼, 160 MB ਦੇ V-ਕੈਸ਼ ਦੇ ਨਾਲ।

- X3D ਵੇਰੀਐਂਟਸ ਵਿੱਚ 32 ਕੋਰ ਤੱਕ ਅਤੇ 448MB ਤੱਕ ਦੇ ਸੰਯੁਕਤ L3 ਕੈਸ਼ ਵਾਲੇ ਡੈਸਕਟੌਪ ਰਾਈਜ਼ਨ ਪ੍ਰੋਸੈਸਰ।

- ਗ੍ਰਿਮਲੌਕ ਪੁਆਇੰਟ ਅਤੇ ਹਾਲੋ: ਜ਼ੈਨ 7/ਜ਼ੈਨ 7ਸੀ ਕੋਰਾਂ ਦਾ ਮਿਸ਼ਰਣ ਅਤੇ 3W 'ਤੇ ਪ੍ਰਦਰਸ਼ਨ-ਪ੍ਰਤੀ-ਵਾਟ ਵਿੱਚ 36% ਤੱਕ ਦੇ ਸੁਧਾਰ।

- TSMC A14 ਨੂੰ ਟਾਰਗੇਟ ਨੋਡ ਵਜੋਂ ਅਤੇ 2027-2028 ਲਈ ਅਨੁਮਾਨਿਤ ਵਿੰਡੋ, ਸੰਭਾਵਿਤ AM5 ਅਨੁਕੂਲਤਾ ਦੇ ਨਾਲ।

ਨਵੀਨਤਮ ਲੀਕ ਇਸ ਵੱਲ ਇਸ਼ਾਰਾ ਕਰਦੇ ਹਨ ਏਐਮਡੀ ਜ਼ੈਨ 7 (ਗ੍ਰੀਮਲਾਕ) ਫਰਮ ਦੇ ਅਗਲੇ ਵੱਡੇ ਕਦਮ ਵਜੋਂ ਉੱਚ-ਪ੍ਰਦਰਸ਼ਨ ਵਾਲਾ CPUਜ਼ਿਆਦਾਤਰ ਡੇਟਾ ਇਸ ਤੋਂ ਆਉਂਦਾ ਹੈ ਮੂਰ ਦਾ ਕਾਨੂੰਨ ਮਰ ਗਿਆ ਹੈ ਅਤੇ, ਹਾਲਾਂਕਿ ਉਹ ਹਾਲੀਆ AMD ਚਾਲਾਂ ਨਾਲ ਫਿੱਟ ਬੈਠਦੇ ਹਨ, ਅਧਿਕਾਰਤ ਪੁਸ਼ਟੀ ਹੋਣ ਤੱਕ ਉਨ੍ਹਾਂ ਨਾਲ ਸਾਵਧਾਨੀ ਨਾਲ ਪੇਸ਼ ਆਉਣਾ ਸਭ ਤੋਂ ਵਧੀਆ ਹੈ।.

ਕਈ ਸਰੋਤਾਂ ਵਿੱਚ ਦੁਹਰਾਈਆਂ ਗਈਆਂ ਮੁੱਖ ਵਿਸ਼ੇਸ਼ਤਾਵਾਂ ਵਿੱਚੋਂ ਪ੍ਰਤੀ ਚਿਪਲੇਟ ਕੋਰਾਂ ਵਿੱਚ ਵਾਧਾ ਹੈ, ਪ੍ਰਤੀ ਕੋਰ L2 ਕੈਸ਼ ਦੁੱਗਣਾ ਕਰੋ ਅਤੇ 3D V-ਕੈਸ਼ ਦੀ ਵਾਪਸੀ ਕਰੋ। ਵਧੇਰੇ ਸਮਰੱਥਾ ਦੇ ਨਾਲ। ਸਪੇਨ ਜਾਂ ਯੂਰਪ ਵਿੱਚ ਅੱਪਡੇਟ ਕਰਨ ਵਾਲਿਆਂ ਲਈ, AM5 ਦੀ ਸੰਭਾਵਿਤ ਨਿਰੰਤਰਤਾ ਇਹ ਮਦਰਬੋਰਡ ਨੂੰ ਬਦਲੇ ਬਿਨਾਂ ਅੱਪਗ੍ਰੇਡ ਕਰਨ ਲਈ ਇੱਕ ਸੰਕੇਤ ਹੋਵੇਗਾ।

ਲੀਕ ਜ਼ੈਨ 7 (ਗ੍ਰੀਮਲਾਕ) ਬਾਰੇ ਕੀ ਪ੍ਰਗਟ ਕਰਦੇ ਹਨ?

ਅਫਵਾਹ ਦਾ ਮੂਲ ਸਾਫ਼ ਹੈ: ਹਰੇਕ ਜ਼ੈਨ 7 ਸੀਸੀਡੀ 16 ਕੋਰਾਂ ਤੱਕ ਏਕੀਕ੍ਰਿਤ ਹੋਵੇਗਾ, ਕੁਝ ਪਿਛਲੇ ਡਿਜ਼ਾਈਨਾਂ ਨਾਲੋਂ ਦੁੱਗਣਾ, ਨਾਲ ਪ੍ਰਤੀ ਕੋਰ 2 MB L2 ਕੈਸ਼ y L3 ਦਾ 64 MB ਪ੍ਰਤੀ ਚਿਪਲੇਟ। ਇਹ ਪਹੁੰਚ ਅੰਦਰੂਨੀ ਬੈਂਡਵਿਡਥ ਅਤੇ ਡੇਟਾ ਨੇੜਤਾ ਨੂੰ ਮਜ਼ਬੂਤ ਕਰਦੀ ਹੈ, ਜੋ ਕਿ AMD ਦੀ ਕੈਸ਼ ਰਣਨੀਤੀ ਦੇ ਥੰਮ੍ਹ ਹਨ।

ਡੈਸਕਟੌਪ ਕੰਪਿਊਟਰਾਂ 'ਤੇ, ਦੋ CCD ਪ੍ਰੋਸੈਸਰਾਂ ਨੂੰ ਆਗਿਆ ਦੇਣਗੇ 32 ਕੋਰ ਤੱਕਰੂਪ X3D ਪ੍ਰਤੀ CCD 160 MB 3D V-Cache ਮੋਜ਼ੇਕ ਜੋੜੇਗਾ।ਪ੍ਰਤੀ ਚਿਪਲੇਟ ਪ੍ਰਭਾਵਸ਼ਾਲੀ L3 ਨੂੰ ਵਧਾ ਕੇ 224 ਮੈਬਾ ਅਤੇ, ਦੋ CCD ਸੰਰਚਨਾਵਾਂ ਵਿੱਚ, ਤੱਕ 448 ਮੈਬਾ ਕੁੱਲ.

ਸਿਲਵਰਟਨ ਅਤੇ ਸਿਲਵਰਕਿੰਗ ਚਿਪਲੇਟਸ: ਸੈਗਮੈਂਟੇਸ਼ਨ ਅਤੇ ਕੈਸ਼ਿੰਗ

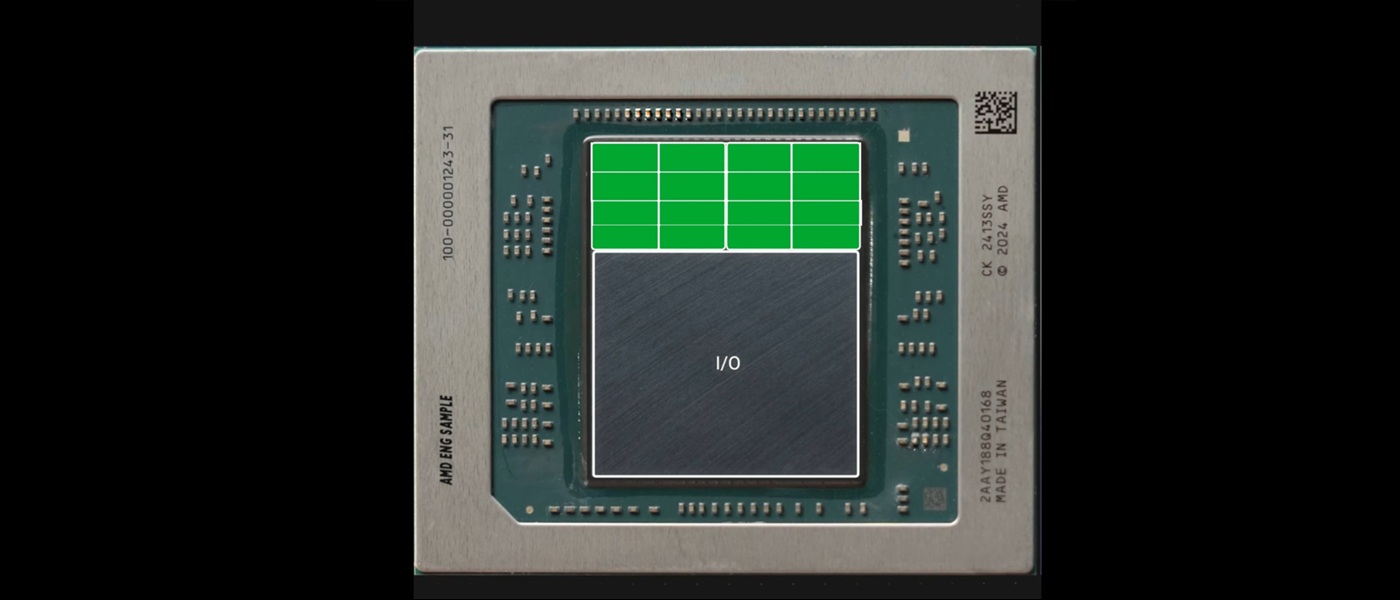

ਗ੍ਰਿਮਲੌਕ ਰੇਂਜ ਯੋਜਨਾ ਨੂੰ ਇਸ ਨਾਲ ਸੰਰਚਿਤ ਕੀਤਾ ਜਾਵੇਗਾ ਦੋ CPU ਚਿੱਪਲੇਟ: ਸਿਲਵਰਟਨ ਅਤੇ ਸਿਲਵਰਕਿੰਗ.

- ਸਿਲਵਰਟਨ ਸਭ ਤੋਂ ਵਧੀਆ ਮਾਡਲ ਹੋਵੇਗਾ, ਜਿਸ ਵਿੱਚ 16 ਕੋਰ ਅਤੇ 32 MB L2 ਕੈਸ਼ ਹੋਵੇਗਾ। (2 MB ਪ੍ਰਤੀ ਕੋਰ), 64 MB L3 ਕੈਸ਼ ਅਤੇ ਸਮਰਥਨ 160 ਐਮਬੀ ਵੀ-ਕੈਸ਼ ਚਿਪਲੇਟ ਵੱਲੋਂ

- ਸਿਲਵਰਕਿੰਗ 3D V-ਕੈਸ਼ ਤੋਂ ਬਿਨਾਂ 8 ਕੋਰ, 16 MB L2 ਕੈਸ਼ ਅਤੇ 32 MB L3 ਕੈਸ਼ ਦੀ ਚੋਣ ਕਰੇਗਾ।.

ਦੋ ਸਿਲਵਰਟਨ ਇੰਜਣਾਂ ਨੂੰ ਜੋੜਨ ਨਾਲ ਟਾਪ-ਆਫ-ਦੀ-ਲਾਈਨ ਸੰਰਚਨਾਵਾਂ ਦਾ ਦਰਵਾਜ਼ਾ ਖੁੱਲ੍ਹ ਜਾਵੇਗਾ 32 ਕੋਰ ਅਤੇ 64 ਥਰਿੱਡਕੁੱਲ L2 ਨੂੰ ਦੁੱਗਣਾ ਕਰਕੇ 64 ਮੈਬਾ ਅਤੇ L3 ਕੈਸ਼ੇਟ ਲਈ ਉਹਨਾਂ ਅੰਕੜਿਆਂ 'ਤੇ ਬਾਰ ਸੈੱਟ ਕਰਨਾ ਜੋ ਹਾਲ ਹੀ ਤੱਕ ਵਿਸ਼ੇਸ਼ ਜਾਪਦੇ ਸਨ ਪੇਸ਼ੇਵਰ ਖੰਡ.

ਅਨੁਮਾਨਿਤ ਉਪਜ ਅਤੇ ਸੀਪੀਆਈ

ਸ਼ੁਰੂਆਤੀ ਅੰਕੜੇ ਇਸ ਦੇ ਵਾਧੇ ਨੂੰ ਦਰਸਾਉਂਦੇ ਹਨ ਸੀਪੀਆਈ ਲਗਭਗ 8% ਕੈਸ਼ ਰੀਡਿਜ਼ਾਈਨ ਦੇ ਕਾਰਨ, ਨਾਲ 16-20% ਦੇ ਵਾਧੂ ਸੁਧਾਰ ਗੈਰ-ਗੇਮਿੰਗ ਵਰਕਲੋਡ ਅਤੇ ਮਹੱਤਵਪੂਰਨ ਮਲਟੀਥ੍ਰੈਡਡ ਸਕੇਲਿੰਗ ਵਿੱਚ। MT ਦ੍ਰਿਸ਼ਾਂ ਵਿੱਚ, ਕਈ ਸਰੋਤ ਦਰਸਾਉਂਦੇ ਹਨ ਜ਼ੈਨ 6 ਦੇ ਮੁਕਾਬਲੇ 67% ਤੱਕਹੋਰ CCD ਕੋਰ, ਬਿਹਤਰ ਕੈਸ਼ ਪ੍ਰਬੰਧਨ ਅਤੇ ਘਣਤਾ ਦੁਆਰਾ ਸਮਰਥਤ।

ਇਹ ਸਭ ਮਾਰਕੀਟਿੰਗ ਬਾਰੇ ਨਹੀਂ ਹੈ: ਜ਼ੋਰ ਲੇਟੈਂਸੀ, ਬੈਂਡਵਿਡਥ, ਅਤੇ ਪੀਕ ਹੈਂਡਲਿੰਗ 'ਤੇ ਹੈ। ਵਿਹਾਰਕ ਸ਼ਬਦਾਂ ਵਿੱਚ, ਇਸਦਾ ਅਨੁਵਾਦ ਹੋ ਸਕਦਾ ਹੈ ਵਧੇਰੇ ਸਥਿਰ ਜਵਾਬ ਸਮਾਂ ਸਮੱਗਰੀ ਸਿਰਜਣਾ, ਸੰਕਲਨ, ਸਿਮੂਲੇਸ਼ਨ, ਅਤੇ ਵਿਸ਼ਲੇਸ਼ਣ ਵਿੱਚ।

ਹੈਂਡਹੈਲਡ ਅਤੇ ਪੋਰਟੇਬਲ ਕੰਸੋਲ: ਗ੍ਰਿਮਲੌਕ ਪੁਆਇੰਟ ਅਤੇ ਹਾਲੋ

ਗਤੀਸ਼ੀਲਤਾ ਵਿੱਚ, ਏ.ਪੀ.ਯੂ. ਗ੍ਰਿਮਲੌਕ ਪੁਆਇੰਟ y ਗ੍ਰਿਮਲੌਕ ਹਾਲੋ ਨਿਊਕਲੀਅਸ ਨੂੰ ਮਿਲਾਏਗਾ ਜ਼ੈਨ 7 ਅਤੇ ਜ਼ੈਨ 7ਸੀ (ਅਤੇ ਇੱਕ "ਘੱਟ-ਪਾਵਰ" ਬਲਾਕ), ਹਾਲੀਆ ਪੀੜ੍ਹੀਆਂ ਦੇ ਫਾਰਮੂਲੇ ਨੂੰ ਦੁਹਰਾਉਂਦੇ ਹੋਏ। ਲਈ ਸੰਰਚਨਾਵਾਂ 'ਤੇ ਵਿਚਾਰ ਕੀਤਾ ਜਾ ਰਿਹਾ ਹੈ 4 ਜ਼ੈਨ 7 + 8 ਜ਼ੈਨ 7c (ਬਿੰਦੂ) ਅਤੇ 8 ਜ਼ੈਨ 7 + 12 ਜ਼ੈਨ 7c (ਹਾਲੋ)।

ਕੁਸ਼ਲਤਾ ਮੁੱਖ ਹੋਵੇਗੀ: ਵਿੱਚ ਸੁਧਾਰ ਪ੍ਰਤੀ ਵਾਟ ਕੁਸ਼ਲਤਾ ਇੱਕ ਤੱਕ 3 ਵਾਟ 'ਤੇ 36%, 7 ਵਾਟ 'ਤੇ 32%, 12 ਵਾਟ 'ਤੇ 25% y 22 ਵਾਟ 'ਤੇ 17%ਇਹ ਸਿੱਧੇ ਤੌਰ 'ਤੇ ਅਲਟਰਾਲਾਈਟ ਉਪਕਰਣਾਂ ਨੂੰ ਪ੍ਰਭਾਵਿਤ ਕਰੇਗਾ ਅਤੇ ਹੈਂਡਹੈਲਡਦੇ ਨਾਲ ਘੱਟ ਫਰੇਮ ਡ੍ਰੌਪ ਅਤੇ ਵਧੇਰੇ ਆਰਾਮਦਾਇਕ ਥਰਮਲ ਪ੍ਰੋਫਾਈਲ।

ਨਿਰਮਾਣ ਅਤੇ ਸਮਾਂ-ਸਾਰਣੀ

CCD ਲਈ, Zen 7 ਨੋਡ ਨੂੰ ਨਿਸ਼ਾਨਾ ਬਣਾਏਗਾ ਟੀਐਸਐਮਸੀ ਏ14, ਇੱਕ ਉੱਨਤ ਵਿਕਾਸ ਜੋ ਕਲਾਸਿਕ "2 nm" ਨਾਮਕਰਨ ਦੀ ਥਾਂ ਲੈਂਦਾ ਹੈ। ਉਦਯੋਗਿਕ ਫਿੱਟ ਇੱਕ ਲੈਂਡਿੰਗ ਦਾ ਸੁਝਾਅ ਦਿੰਦਾ ਹੈ ਜੋ, ਉਤਪਾਦ ਦੇ ਅਧਾਰ ਤੇ, ਇਹ ਮੋਬਾਈਲ ਲਈ 2027 ਦੇ ਅੰਤ ਤੋਂ ਲੈ ਕੇ ਡੈਸਕਟੌਪ ਅਤੇ ਡੇਟਾ ਸੈਂਟਰ ਲਈ 2028 ਤੱਕ ਹੋ ਸਕਦਾ ਹੈ।.

ਇਹ ਗਤੀ ਦੋ-ਸਾਲਾ ਰੀਲੀਜ਼ ਕੈਡੈਂਸ ਅਤੇ ਅਤਿ-ਆਧੁਨਿਕ ਨੋਡਾਂ ਦੀ ਪਰਿਪੱਕਤਾ ਦੇ ਅਨੁਸਾਰ ਹੈ, ਜੋ ਕਿ ਇਸ ਵਿੱਚ ਵੀ ਧਿਆਨ ਦੇਣ ਯੋਗ ਹੈ ਨਿਰਮਾਣ ਲਾਗਤ ਅਤੇ ਵਿੱਚ ਕੰਪਿਊਟ ਦੇ ਨੇੜੇ ਹੋਰ ਮੈਮੋਰੀ ਨੂੰ ਜੋੜਨ ਦੀ ਜਟਿਲਤਾ.

ਏਆਈ ਪਲੇਟਫਾਰਮ, ਆਈਐਸਏ, ਅਤੇ ਵਿਸ਼ੇਸ਼ਤਾਵਾਂ

ਕਈ ਸਰੋਤ ਸੰਭਾਵਿਤ ਵੱਲ ਇਸ਼ਾਰਾ ਕਰਦੇ ਹਨ AM5 ਅਨੁਕੂਲਤਾਜੇਕਰ ਇਹ ਫੈਸਲਾ ਪੁਸ਼ਟੀ ਹੋ ਜਾਂਦਾ ਹੈ, ਤਾਂ ਯੂਰਪੀਅਨ ਰਿਟੇਲ ਚੈਨਲ ਵਿੱਚ ਗੋਦ ਲੈਣ ਦੀ ਸਹੂਲਤ ਮਿਲੇਗੀ। ਹਦਾਇਤ ਪੱਧਰ 'ਤੇ, ਇੱਕ ਨਵਾਂ ISA ਸੈੱਟ ਐਕਸਲੇਟਰਾਂ ਲਈ ਕੁਆਂਟਾਇਜ਼ੇਸ਼ਨ ਸਹਾਇਤਾ ਅਤੇ ਡੇਟਾ ਤਿਆਰੀ ਵਿੱਚ ਸੁਧਾਰਾਂ ਦੇ ਨਾਲ.

ਇਸ ਤੋਂ ਇਲਾਵਾ, AMD ਪਹਿਲਾਂ ਹੀ ਅਧਿਕਾਰਤ ਤੌਰ 'ਤੇ ਜ਼ੈਨ 7 ਦਾ ਜ਼ਿਕਰ ਕੀਤਾ ਗਿਆ ਇਸਦੇ ਰੋਡਮੈਪ ਵਿੱਚ, ਇੱਕ ਦੀ ਉਮੀਦ ਕਰਦੇ ਹੋਏ ਮੈਟ੍ਰਿਕਸ ਮੋਟਰ ਅਤੇ ਕੋਰਾਂ ਵਿੱਚ ਏਕੀਕ੍ਰਿਤ ਵਿਸ਼ਾਲ AI ਡੇਟਾ ਫਾਰਮੈਟ। ਇਹ ਪਹੁੰਚ AVX-512 ਤੋਂ ਪਰੇ ਹੈ: ਟੀਚਾ ਅਨੁਮਾਨ ਅਤੇ ਪ੍ਰੀ/ਪੋਸਟ-ਪ੍ਰੋਸੈਸਿੰਗ ਨੂੰ ਤੇਜ਼ ਕਰਨਾ ਹੈ। ਜਨਰਲਿਸਟ ਸੀਪੀਯੂ.

ਸਰਵਰ ਅਤੇ ਪੇਸ਼ੇਵਰ ਸਕੇਲਿੰਗ

EPYC ਖੇਤਰ ਵਿੱਚ, ਗ੍ਰਿਮਲੌਕ ਆਰਕੀਟੈਕਚਰ ਦੀ ਭਾਲ ਕਰੇਗਾ ਕੋਰ ਅਤੇ ਕੈਸ਼ ਵਿੱਚ ਸਕੇਲਿੰਗ ਚਿਪਲੇਟ ਫ਼ਲਸਫ਼ੇ ਨੂੰ ਕਾਇਮ ਰੱਖਣਾਵਿਸ਼ਲੇਸ਼ਣਾਤਮਕ ਅਤੇ ਡੇਟਾਬੇਸ ਵਰਕਲੋਡ ਲਈ ਮੁੱਖ ਕਾਰਕ, ਇਕਸਾਰ ਲੇਟੈਂਸੀ ਅਤੇ ਵਿਆਪਕ L3 ਪਹੁੰਚ ਨੂੰ ਤਰਜੀਹ ਦਿੱਤੀ ਜਾਵੇਗੀ। ਯੂਰਪੀ ਡੇਟਾ ਸੈਂਟਰ.

ਹਾਲਾਂਕਿ ਫਿਲਟਰੇਸ਼ਨ ਦੇ ਆਧਾਰ 'ਤੇ ਸਹੀ ਗਿਣਤੀ ਬਦਲਦੀ ਹੈ, ਦਿਸ਼ਾ ਸਪੱਸ਼ਟ ਹੈ: ਪ੍ਰਤੀ CCD ਵਧੇਰੇ ਘਣਤਾ, ਵੱਡਾ V-ਕੈਸ਼ ਅਤੇ ਤੀਬਰ ਡੇਟਾ ਟ੍ਰੈਫਿਕ ਦਾ ਸਮਰਥਨ ਕਰਨ ਲਈ ਅੰਦਰੂਨੀ ਮਾਰਗਾਂ ਨੂੰ ਸੁਧਾਰਿਆ ਗਿਆ।

ਜੇਕਰ ਯੋਜਨਾਵਾਂ ਇਕਸਾਰ ਹੁੰਦੀਆਂ ਹਨ, ਜ਼ੈਨ 7 AMD ਦੇ "ਕੈਸ਼-ਫਸਟ" ਮਾਡਲ ਨੂੰ ਇਕਜੁੱਟ ਕਰਦਾ ਹੋਇਆ ਆਵੇਗਾ: 16-ਕੋਰ ਸੀਸੀਡੀ, ਡੁਪਲੀਕੇਟ L2, ਸਟੀਰੌਇਡ 'ਤੇ V-ਕੈਸ਼, ਅਤੇ AI ਅਤੇ ਕੁਸ਼ਲਤਾ ਵਿੱਚ ਸਪੱਸ਼ਟ ਵਾਧਾਸਪੇਨ ਅਤੇ ਯੂਰਪ ਦੇ ਉਪਭੋਗਤਾਵਾਂ ਲਈ, ਕਾਲਪਨਿਕ AM5 ਨਿਰੰਤਰਤਾ ਅਤੇ ਪ੍ਰਤੀ ਵਾਟ ਪ੍ਰਦਰਸ਼ਨ 'ਤੇ ਧਿਆਨ ਕੇਂਦਰਿਤ ਕਰਨ ਨਾਲ ਗ੍ਰਿਮਲੌਕ ਨੂੰ ਬਿਨਾਂ ਕਿਸੇ ਧੂਮ-ਧਾਮ ਦੇ, ਪਰ ਮਹੱਤਵਪੂਰਨ ਤਕਨੀਕੀ ਬੁਨਿਆਦ ਦੇ ਨਾਲ, ਤਰਕਸ਼ੀਲ ਅੱਪਗ੍ਰੇਡਾਂ ਲਈ ਰਾਡਾਰ 'ਤੇ ਰੱਖਿਆ ਜਾਂਦਾ ਹੈ।

ਮੈਂ ਇੱਕ ਤਕਨਾਲੋਜੀ ਉਤਸ਼ਾਹੀ ਹਾਂ ਜਿਸਨੇ ਆਪਣੀਆਂ "ਗੀਕ" ਰੁਚੀਆਂ ਨੂੰ ਇੱਕ ਪੇਸ਼ੇ ਵਿੱਚ ਬਦਲ ਦਿੱਤਾ ਹੈ। ਮੈਂ ਆਪਣੀ ਜ਼ਿੰਦਗੀ ਦੇ 10 ਤੋਂ ਵੱਧ ਸਾਲ ਅਤਿ-ਆਧੁਨਿਕ ਤਕਨਾਲੋਜੀ ਦੀ ਵਰਤੋਂ ਕਰਦੇ ਹੋਏ ਅਤੇ ਸ਼ੁੱਧ ਉਤਸੁਕਤਾ ਨਾਲ ਹਰ ਕਿਸਮ ਦੇ ਪ੍ਰੋਗਰਾਮਾਂ ਨਾਲ ਟਿੰਕਰਿੰਗ ਵਿੱਚ ਬਿਤਾਏ ਹਨ। ਹੁਣ ਮੈਂ ਕੰਪਿਊਟਰ ਤਕਨਾਲੋਜੀ ਅਤੇ ਵੀਡੀਓ ਗੇਮਾਂ ਵਿੱਚ ਮੁਹਾਰਤ ਹਾਸਲ ਕਰ ਲਈ ਹੈ। ਇਹ ਇਸ ਲਈ ਹੈ ਕਿਉਂਕਿ ਮੈਂ 5 ਸਾਲਾਂ ਤੋਂ ਵੱਧ ਸਮੇਂ ਤੋਂ ਟੈਕਨਾਲੋਜੀ ਅਤੇ ਵੀਡੀਓ ਗੇਮਾਂ 'ਤੇ ਵੱਖ-ਵੱਖ ਵੈੱਬਸਾਈਟਾਂ ਲਈ ਲਿਖ ਰਿਹਾ ਹਾਂ, ਲੇਖ ਤਿਆਰ ਕਰ ਰਿਹਾ ਹਾਂ ਜੋ ਤੁਹਾਨੂੰ ਅਜਿਹੀ ਭਾਸ਼ਾ ਵਿੱਚ ਲੋੜੀਂਦੀ ਜਾਣਕਾਰੀ ਦੇਣ ਦੀ ਕੋਸ਼ਿਸ਼ ਕਰਦਾ ਹੈ ਜੋ ਹਰ ਕੋਈ ਸਮਝ ਸਕਦਾ ਹੈ।

ਜੇਕਰ ਤੁਹਾਡੇ ਕੋਈ ਸਵਾਲ ਹਨ, ਤਾਂ ਮੇਰਾ ਗਿਆਨ ਵਿੰਡੋਜ਼ ਓਪਰੇਟਿੰਗ ਸਿਸਟਮ ਦੇ ਨਾਲ-ਨਾਲ ਮੋਬਾਈਲ ਫੋਨਾਂ ਲਈ ਐਂਡਰਾਇਡ ਨਾਲ ਸਬੰਧਤ ਹਰ ਚੀਜ਼ ਤੋਂ ਹੈ। ਅਤੇ ਮੇਰੀ ਵਚਨਬੱਧਤਾ ਤੁਹਾਡੇ ਪ੍ਰਤੀ ਹੈ, ਮੈਂ ਹਮੇਸ਼ਾ ਕੁਝ ਮਿੰਟ ਬਿਤਾਉਣ ਅਤੇ ਇਸ ਇੰਟਰਨੈਟ ਦੀ ਦੁਨੀਆ ਵਿੱਚ ਤੁਹਾਡੇ ਕਿਸੇ ਵੀ ਪ੍ਰਸ਼ਨ ਨੂੰ ਹੱਲ ਕਰਨ ਵਿੱਚ ਤੁਹਾਡੀ ਮਦਦ ਕਰਨ ਲਈ ਤਿਆਰ ਹਾਂ।