- CCD med upp till 16 kärnor, L2-cache på 2 MB per kärna och L3-cache på 64 MB per CCD, med en V-cache på 160 MB.

- Stationära Ryzen-processorer med upp till 32 kärnor och upp till 448 MB kombinerad L3-cache i X3D-varianter.

- Grimlock Point och Halo: en blandning av Zen 7/Zen 7c-kärnor och prestandaförbättringar per watt på upp till 36 % vid 3 W.

- TSMC A14 som målnod och uppskattat fönster mot 2027-2028, med möjlig AM5-kompatibilitet.

De senaste läckorna pekar på AMD Zen 7 (Grimlock) som företagets nästa stora steg i högpresterande CPUMerparten av informationen kommer från Moores lag är död Och även om de passar in i AMD:s senaste drag, Det är bäst att behandla dem med försiktighet tills det finns en officiell bekräftelse..

Bland de viktigaste funktionerna som upprepas i flera källor finns ökningen av kärnor per chiplet, Dubbel L2-cache per kärna och återkomsten av 3D V-cache med större kapacitet. För de som uppdaterar i Spanien eller Europa, möjlig fortsättning på AM5 Det skulle vara en nickning till uppgraderingar utan att behöva byta moderkort.

Vad avslöjar läckorna om Zen 7 (Grimlock)?

Kärnan i ryktet är tydlig: Varje Zen 7 CCD skulle integrera upp till 16 kärnor, dubbelt så mycket som vissa tidigare designer, med 2 MB L2 per kärna y 64MB L3 per chiplet. Denna metod förstärker intern bandbredd och datanärhet, grundpelare i AMD:s cachestrategi.

På stationära datorer skulle två CCD-kretsar tillåta processorer på upp till 32 kärnorVarianterna X3D skulle lägga till upp till 160 MB 3D V-Cache-mosaik per CCDökar den effektiva L3 per chiplet till 224 MB och, i två CCD-konfigurationer, upp till 448 MB totalt.

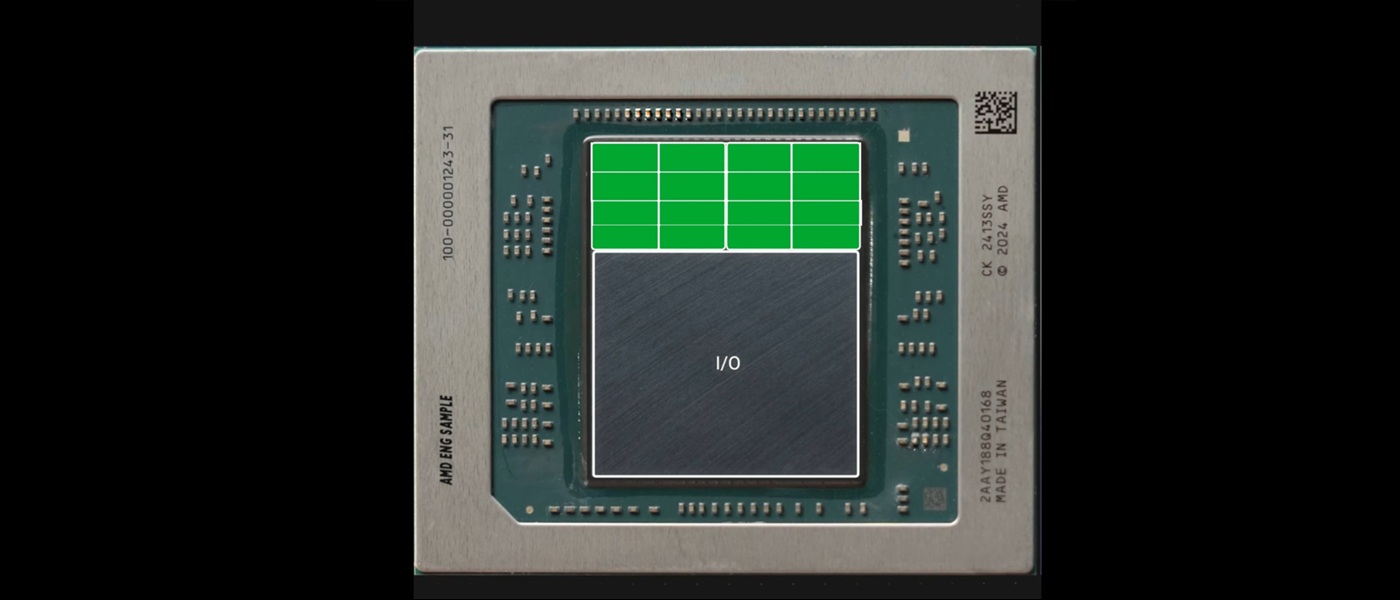

Silverton- och Silverking-chiplets: segmentering och cachning

Grimlock-områdesplanen skulle struktureras med två CPU-chiplets: Silverton och Silverking.

- Silverton skulle vara toppmodellen, med 16 kärnor och 32 MB L2-cache. (2 MB per kärna), 64 MB L3-cache och stöd för 160 MB V-cache av chiplet

- Silverking skulle välja 8 kärnor, 16 MB L2-cache och 32 MB L3-cache, utan 3D V-cache..

Att kombinera två Silverton-motorer skulle öppna dörren till toppmoderna konfigurationer med 32 kärnor och 64 trådarfördubbling av den totala L2 till 64 MB och sätter ribban för L3-prestanda vid siffror som fram till nyligen verkade exklusiva för professionellt segment.

Beräknad avkastning och KPI

Preliminära siffror indikerar en ökning av KPI runt 8 % på grund av omdesignen av cachen, med ytterligare förbättringar på 16–20 % i arbetsbelastningar som inte rör spel och betydande flertrådad skalning. I MT-scenarier indikerar flera källor upp till 67 % jämfört med Zen 6stöds av fler CCD-kärnor, bättre cachehantering och densitet.

Det handlar inte bara om marknadsföring: tonvikten ligger på latens, bandbredd och hantering av toppar. I praktiken skulle detta kunna innebära mer stabila svarstider inom innehållsskapande, sammanställning, simulering och analys.

Handhållna och bärbara konsoler: Grimlock Point och Halo

Inom mobilitet, APU:erna Grimlock Point y Grimlock Halo skulle blanda kärnor Zen 7 och Zen 7c (och ett "lågeffektblock"), vilket upprepar formeln från senare generationer. Konfigurationer övervägs för 4 Zen 7 + 8 Zen 7c (Punkt) och 8 Zen 7 + 12 Zen 7c (Halo).

Effektivitet skulle vara nyckeln: förbättringar i prestanda per watt upp till en 36 % vid 3 W, 32 % vid 7 W, 25 % vid 12 W y 17 % vid 22 WDetta skulle direkt påverka ultralätt utrustning och handen, med färre bildfall och bekvämare termiska profiler.

Tillverkning och schemaläggning

För CCD:er skulle Zen 7 rikta in sig på noden TSMC A14, en avancerad utveckling som ersätter den klassiska "2 nm"-nomenklaturen. Den industriella anpassningen antyder en landning som, beroende på produkt, Det kan sträcka sig från slutet av 2027 för mobila enheter till 2028 för datorer och datacenter..

Denna takt ligger i linje med en tvåårig lanseringskadens och mognaden hos de banbrytande noderna, något som också märks i Tillverkningskostnad och i komplexiteten i att integrera mer minne närmare beräkningssystemet.

AI-plattform, ISA och funktioner

Flera källor pekar på den möjliga AM5-kompatibilitetDetta beslut, om det bekräftas, skulle underlätta införandet i den europeiska detaljhandelskanalen. På instruktionsnivå, en ny ISA-uppsättning med kvantiseringsstöd och förbättringar i dataförberedelse för acceleratorer.

Dessutom har AMD redan officiellt nämnda Zen 7 i sin färdplan, i väntan på en matrismotor och bredare AI-dataformat integrerade i kärnorna. Tillvägagångssättet går bortom AVX-512: målet är att accelerera inferens och för-/efterbehandling inom Generalist-CPU.

Servrar och professionell skalning

Inom EPYC-fältet skulle Grimlock-arkitekturen söka skalning i kärnor och cache upprätthålla chiplet-filosofinKonsekvent latens och bredare L3-åtkomst skulle prioriteras, viktiga faktorer för analytiska och databasbaserade arbetsbelastningar. Europeiska datacenter.

Även om de exakta siffrorna ändras beroende på filtreringen är riktningen tydlig: mer densitet per CCD, Större V-cache och förfinade interna vägar för att stödja intensiv datatrafik.

Om planerna stämmer överens, Zen 7 kommer att anlända och konsolidera AMD:s "cache-first"-modell: 16-kärnig CCD, Duplicerat L2, V-Cache på steroider och en tydlig ökning av AI och effektivitetFör användare i Spanien och Europa, den hypotetiska AM5-kontinuitet Och fokuset på prestanda per watt sätter Grimlock på radarn för välgrundade uppgraderingar, utan ståhej, men med en rejäl teknisk grund.

Jag är en teknikentusiast som har gjort sina "nördar"-intressen till ett yrke. Jag har tillbringat mer än 10 år av mitt liv med att använda den senaste tekniken och mixtrat med alla typer av program av ren nyfikenhet. Nu har jag specialiserat mig på datateknik och tv-spel. Detta beror på att jag i mer än 5 år har arbetat med att skriva för olika webbplatser om teknik och videospel, skapa artiklar som försöker ge dig den information du behöver på ett språk som är begripligt för alla.

Om du har några frågor sträcker sig min kunskap från allt som rör operativsystemet Windows samt Android för mobiltelefoner. Och mitt engagemang är för dig, jag är alltid villig att spendera några minuter och hjälpa dig att lösa alla frågor du kan ha i den här internetvärlden.