- C‑States ahorran en reposo (más profundos = más latencia), P‑States ajustan frecuencia/voltaje bajo carga.

- Ambos son ortogonales: la CPU puede dormir profundo tras ejecutar a alta frecuencia.

- Latencias de C6/C7 impactan en juegos, audio y red; ajusta el C‑State máximo según la carga.

- Usa herramientas (Windows y Linux) y perfiles BIOS/OS para medir y gobernar sin perder estabilidad.

En los procesadores modernos, la gestión de energía no es un único interruptor, sino un conjunto de mecanismos coordinados (C-States y P-States de la CPU, entre otros) que el sistema operativo, el firmware y la propia CPU usan para ajustar consumo, temperatura y rendimiento en tiempo real. Este artículo destila y organiza esa maraña de siglas para que puedas entender qué ocurre bajo el capó cuando tu equipo ahorra energía o acelera.

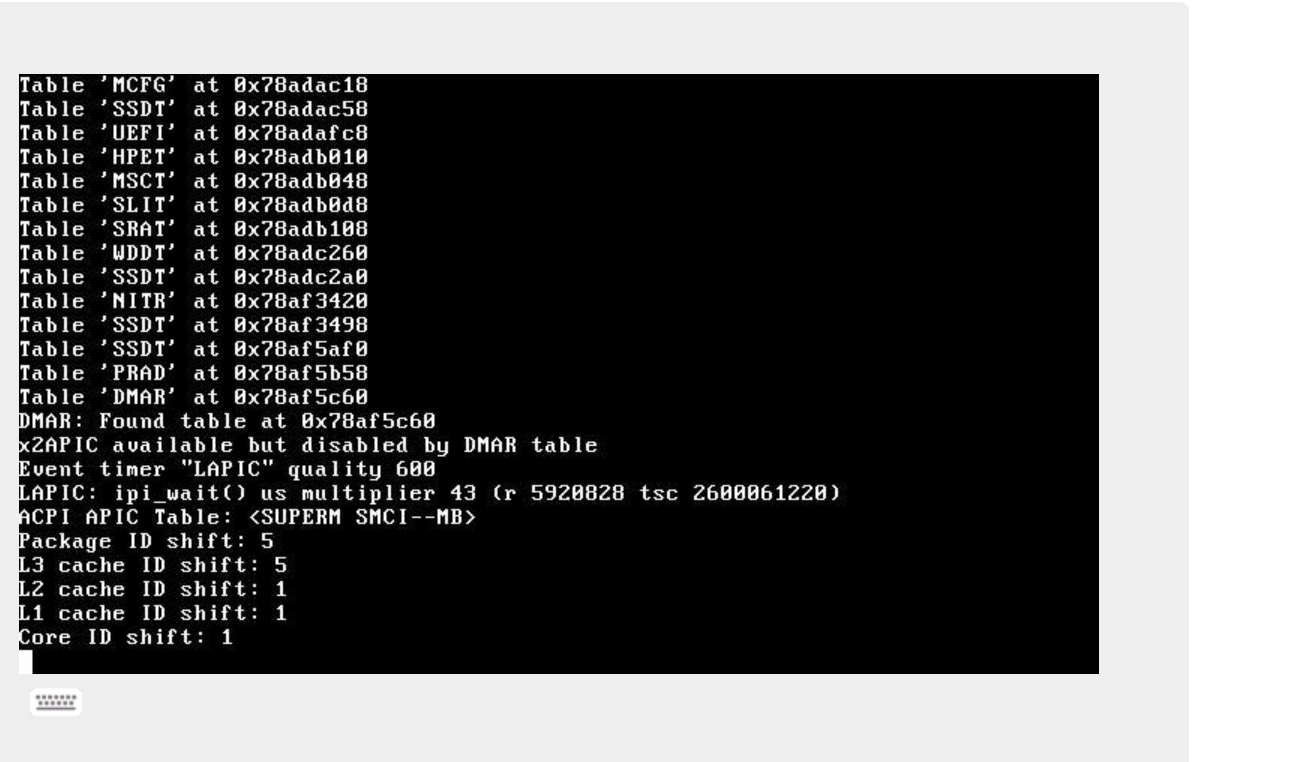

Aunque cada fabricante y familia de CPU añade su toque, la base es común: ACPI define “estados” estándar para el sistema, los dispositivos y el procesador. Aquí verás las diferencias entre C‑States y P‑States, cómo se relacionan con G/S/D‑States, qué impacto real tienen en latencia, por qué los jugadores y el audio pro suelen desactivar reposos profundos, y qué herramientas práctivas hay en Windows, Linux y entornos como ESXi.

ACPI en pocas palabras

ACPI (Advanced Configuration and Power Interface) es el estándar que orquesta la energía en PCs y servidores, y que sustituyó a APM con mayor control y granularidad. Nació de la mano de Intel, Microsoft y Toshiba en los 90 y evolucionó para abarcar 64‑bit, multiprocesamiento, buses modernos (PCIe, SATA, USB 3.x) y detección de eventos (por ejemplo, el botón de encendido).

Aunque ACPI reina sobre todo en la familia x86, también se ha desplegado en otras arquitecturas. En móviles ARM, sin embargo, se usan estrategias propias (como big.LITTLE y clústeres heterogéneos) para balancear eficiencia y respuesta dependiendo de la carga.

Estados globales y de suspensión (G‑States y S‑States)

Los estados globales describen la situación completa del sistema. El más importante es G0/S0 (Working), donde el equipo está activo. En hardware reciente existe S0ix (subestados de S0) que permiten modos de reposo muy finos con parte del SoC durmiendo, especialmente en portátiles.

- G0/S0: sistema en funcionamiento.

- G1 (Sleeping): abarca S1, S2, S3 (suspensión a RAM) y S4 (hibernación a disco). S3 mantiene alimentada la RAM para reanudar rápido; S4 vuelca la memoria a almacenamiento no volátil.

- G2/S5 (Soft‑off): apagado lógico con alimentación mínima para permitir despertar por eventos (teclado, red, etc.).

- G3 (Mechanical‑off): apagado físico; solo sobrevive el RTC por pila.

Ten presente que las C‑States del procesador viven dentro de G0/S0: cuando el sistema entra en G1, el paquete de la CPU se apaga y los C‑States dejan de jugar.

Estados de dispositivo (D‑States)

ACPI también perfila cómo duermen o se encienden los periféricos. D0 equivale a “operativo a tope”, D1/D2 son intermedios (dependen del dispositivo) y D3 se bifurca en Hot (con alimentación auxiliar, responde al bus) o Cold (apagado total, no responde). Esto permite, por ejemplo, que una tarjeta de red despierte el equipo mientras otros dispositivos siguen dormidos.

T‑States: modulación por reloj, el último recurso

Además de P y C, existe la modulación por reloj (T‑States): una especie de PWM que suprime pulsos del reloj interno en un patrón (por ejemplo, 1 de cada 8), reduciendo actividad sin cambiar la frecuencia base anunciada. Está pensada como contramedida térmica o de emergencia (PROCHOT) y se controla vía IA32_CLOCK_MODULATION, con causas/logs en MSR_*_PERF_LIMIT_REASONS.

Aunque algunos documentos la den por “irrelevante”, en la práctica sigue apareciendo en portátiles con diseño térmico justo y bajo cargas sostenidas. Si ves que Windows reporta una “velocidad” por debajo del mínimo EIST, probablemente hay T‑State activo (gating de reloj).

M‑States: ahorro en memoria

ACPI también contempla estados de memoria para reducir consumo del subsistema DRAM cuando el sistema está ocioso. M0 es operación normal; M1/M2 y otros modos llevan la memoria a self‑refresh y temporizaciones relajadas, recortando energía con latencias de reactivación mayores. Son menos visibles para el usuario, pero contribuyen al ahorro total.

C‑States del procesador: dormir con cabeza

Vamos ya a abordar le tema del artículo: C-States y P-States. Los C‑States son los estados de inactividad del núcleo o del paquete. Cuanto mayor el número, más profundo el sueño y más ahorro, pero también mayor latencia al despertar. Se solicitan con instrucciones privilegiadas como HLT o MWAIT (esta última puede pedir explícitamente un Cx y subestado), y el mapeo de capacidades llega al SO vía ACPI (_CST).

- C0: ejecución normal. Aquí es donde entran en juego los P‑States.

- C1/C1E (Halt): el core se detiene, vuelta casi instantánea a C0; C1E reduce más consumo.

- C2 (Stop‑Clock): se detienen señales de reloj, el retorno tarda algo más.

- C3 (Sleep/Deep Sleep): se vacían L1/L2 a la última caché (LLC) y se apagan relojes centrales; solo se conserva el estado esencial del núcleo.

- C6 y superiores: el núcleo puede apagarse y guardar su contexto en SRAM dedicada, llevando el voltaje del core a ~0 V; al salir se restaura ese estado. Algunos modelos exponen hasta C10 en plataformas recientes.

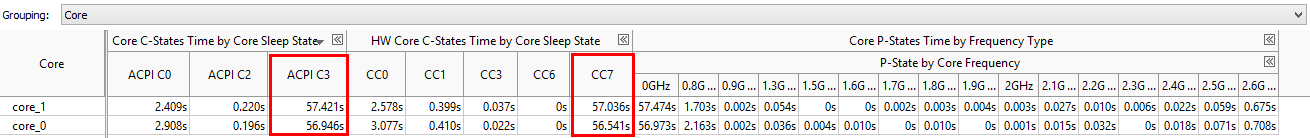

Además de los C‑States por núcleo (CC‑states), existe el plano de Package C‑States (PC‑states) que apagan bloques compartidos (como la LLC) cuando todos los cores lo permiten. Hay combinaciones inválidas (si un core está en C0, el paquete no puede estar en PC6), y la CPU puede “promocionar” o “degradar” automáticamente el nivel según latencias y residencias objetivo.

La latencia importa: C1 se abandona en muy pocas decenas de ciclos, mientras que C6/C7 pueden costar cientos de microsegundos. De ahí que carga sensible al retardo (juegos, audio en tiempo real, networking exigente) sufra si el procesador cae en reposos profundos con frecuencia.

P‑States de rendimiento: frecuencia y voltaje

Mientras los C‑States son “dormir cuando no hay trabajo”, los P‑States son “ajustar el ritmo cuando sí hay trabajo, pero no hace falta el máximo”. P0 es el estado de mayor rendimiento (frecuencia/voltaje más altos) y luego vienen P1, P2… cada uno con pares frecuencia‑voltaje decrecientes. Estas tablas se declaran al SO vía ACPI (_PSS) y se controlan por MSRs como IA32_PERF_CTL/IA32_PERF_STATUS.

Históricamente el sistema operativo pedía P‑States (EIST/SpeedStep en Intel, PowerNow! en AMD), pero hoy es común el Hardware‑controlled Performance States (HWP/Speed Shift): el SO indica una preferencia (rendimiento/ahorro) y la CPU decide en milisegundos el punto exacto, con una granularidad per‑core muy fina.

Un detalle clave: P‑States y C‑States son “ortogonales”. Puedes estar en P0 (frecuencia alta) y, al quedar inactivo, entrar en C6. Al revés, bajo carga sostenida a P2 no hay C‑States porque el core está ejecutando (C0). Por eso conviene separar mentalmente “frecuencia/voltaje” (P) de “reposo” (C).

De APM a ACPI: cambio de paradigma

APM fue la API previa gestionada principalmente desde BIOS y drivers. Permitía apagar periféricos inactivos y definir estados globales simples, pero la CPU quedaba fuera del control directo del SO por seguridad. ACPI dio el salto a un modelo más rico y estandarizado, con descripciones en tablas, control granular y colaboración estrecha entre firmware, SO y hardware.

Cómo se entra y se sale de los C‑States

Cuando el planificador no tiene hilos listos, ejecuta HLT o MWAIT con una pista del C‑State objetivo; las interrupciones “rompen” el sueño y devuelven al core a C0. En C3 se vacían cachés privadas; en C6 se guarda contexto a SRAM y se baja el voltaje a cero. Algunas CPUs implementan Power Aware Interrupt Routing (PAIR) para dirigir interrupciones a núcleos ya activos (para ahorrar) o a núcleos ociosos (para rendimiento), según convenga.

Turbo, TDP y límites de potencia

Los procesadores definen un TDP que el sistema de refrigeración debe poder disipar sostenidamente (PL1: potencia media segura). Por encima, pueden entrar ventanas de potencia más altas (PL2, y niveles adicionales como PL3/PL4 según plataforma) durante periodos acotados. Si hay margen térmico y eléctrico, el núcleo puede superar la frecuencia base vía Turbo, incluso de forma asimétrica (más turbo con menos núcleos activos).

Cuando las temperaturas exceden el umbral o el VRM/potencia lo exige, puede activarse PROCHOT y entrar T‑State o recorte de frecuencia para proteger el chip. Este comportamiento es común en portátiles finos.

Windows: planes de energía, lecturas y contadores

Windows ofrece planes como “Ahorro de energía”, “Equilibrado” y “Alto rendimiento”. El primero tiende a bajar P‑States con agresividad y dormir profundo; el tercero mantiene frecuencias altas y evita caídas de latencia sacrificando eficiencia. “Equilibrado” intenta una vía media.

En el Administrador de tareas, la “velocidad” es una métrica sintética que promedia por core y considera el duty de modulación si hay T‑States. Puede superar la base (Turbo) o caer por debajo del mínimo EIST (gating). Para telemetría avanzada, el contador “\Processor Information(_Total)\% Processor Performance” refleja el porcentaje de rendimiento efectivo según la CPU.

Existen utilidades para diagnosticar o ajustar: CPU‑Z (datos básicos), HWiNFO (sensores), ThrottleStop (clocks, C‑States por core y control de PROCHOT/modulación), o ParkControl (afinado de aparcamiento de núcleos/C‑States) que tocan los parámetros ocultos del plan de energía (powercfg permite editar “IDLE_PROMOTE/DEMOTE”, etc.).

Linux: cpupower, turbostat y CoreFreq

En Linux, herramientas como cpupower muestran gobernadores, rangos de frecuencia y latencias de transición; turbostat expone MSRs, razones de límites (MSR_CORE_PERF_LIMIT_REASONS) y residencias por C‑State; y CoreFreq ofrece una vista detallada de frecuencias absolutas, C‑States y Turbo por core/paquete.

Un matiz práctico: en algunos equipos, el driver intel_idle puede ignorar restricciones de BIOS sobre C‑States y usar su propia tabla. En otros, el firmware “bloquea” vía MSR el C‑State más profundo permitido para el SO.

BIOS/UEFI y perfiles: quién manda de verdad

En la configuración de BIOS/UEFI suelen aparecer interruptores clave: EIST/SpeedStep, TurboBoost y CPU C‑States. Además, muchos servidores permiten elegir perfiles de energía: “Maximum Performance” (todo al máximo, latencias mínimas) o “OS Controlled/Custom”, donde el hipervisor o SO gobierna P/C‑States. Seleccionar “OS Control Mode” delega la inteligencia al sistema operativo.

Si usas hipervisores como ESXi, es buena idea combinar OS Control Mode en BIOS con el plan “High Performance” del hipervisor cuando el objetivo es exprimir rendimiento (por ejemplo con NSX‑T, Edge Nodes o funciones sensibles a latencia). En ese escenario verás P‑State 0 con más frecuencia y C‑States limitados a C0/C1; con un plan “Balanced”, el host se apoyará más en P‑States bajos y C‑States más profundos.

A modo de resumen para todo este lío de C-States y P-States: ACPI define el marco, C‑States ahorran cuando no hay trabajo, P‑States ajustan el “marcha larga/corta” bajo carga, T‑States salvan los muebles en calor extremo, y M‑States quitan vatios a la memoria. La clave está en escoger el perfil adecuado a tu uso, medir con las herramientas correctas y, si hace falta, poner límites sensatos a la profundidad de reposo.

Redactor especializado en temas de tecnología e internet con más de diez años de experiencia en diferentes medios digitales. He trabajado como editor y creador de contenidos para empresas de comercio electrónico, comunicación, marketing online y publicidad. También he escrito en webs de economía, finanzas y otros sectores. Mi trabajo es también mi pasión. Ahora, a través de mis artículos en Tecnobits, intento explorar todas las novedades y nuevas oportunidades que el mundo de la tecnología nos ofrece día a día para mejorar nuestras vidas.