- CCD de hasta 16 núcleos, L2 de 2 MB por núcleo y L3 de 64 MB por CCD, con V‑Cache de 160 MB.

- Ryzen de sobremesa de hasta 32 núcleos y hasta 448 MB de caché L3 combinada en variantes X3D.

- Grimlock Point y Halo: mezcla de núcleos Zen 7/Zen 7c y mejoras de rendimiento por vatio de hasta un 36% a 3 W.

- TSMC A14 como nodo objetivo y ventana estimada hacia 2027‑2028, con posible compatibilidad AM5.

Las últimas filtraciones apuntan a AMD Zen 7 (Grimlock) como el próximo gran paso de la firma en CPU de alto rendimiento. La mayoría de datos llegan de Moore’s Law Is Dead y, aunque encajan con movimientos recientes de AMD, conviene cogerlos con cautela hasta que haya confirmación oficial.

Entre las claves repetidas en varias fuentes destacan el salto en núcleos por chiplet, el doble de caché L2 por núcleo y el regreso de 3D V‑Cache con más capacidad. Para quien actualiza en España o Europa, la posible continuidad de AM5 sería un guiño a las actualizaciones sin tener que cambiar de placa.

Qué adelantan las filtraciones de Zen 7 (Grimlock)

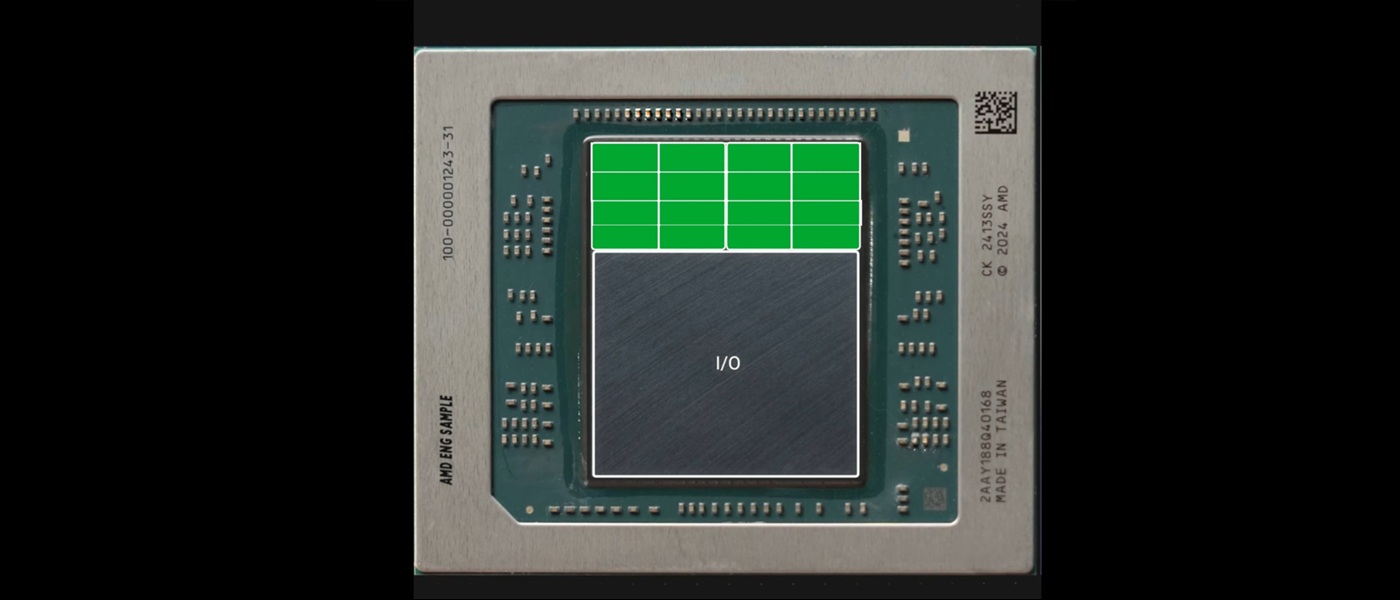

El corazón del rumor es claro: cada CCD de Zen 7 integraría hasta 16 núcleos, el doble que en ciertos diseños previos, con 2 MB de L2 por núcleo y 64 MB de L3 por chiplet. Este enfoque refuerza el ancho de banda interno y la cercanía de datos, pilares de la estrategia de caché de AMD.

En sobremesa, dos CCD permitirían procesadores de hasta 32 núcleos. Las variantes X3D sumarían un mosaico de 160 MB de 3D V‑Cache por CCD, elevando la L3 efectiva por chiplet a 224 MB y, en configuraciones de dos CCD, hasta 448 MB en total.

Chiplets Silverton y Silverking: segmentación y caché

El plan de gama Grimlock se articularía con dos chiplets CPU: Silverton y Silverking.

- Silverton sería el tope de gama, con 16 núcleos, 32 MB de L2 (2 MB por núcleo), 64 MB de L3 y soporte para V‑Cache de 160 MB por chiplet

- Silverking apostaría por 8 núcleos, 16 MB de L2 y 32 MB de L3, sin 3D V‑Cache.

Combinando dos Silverton se abriría la puerta a configuraciones tope con 32 núcleos y 64 hilos, doblando también la L2 total hasta 64 MB y dejando el listón de caché L3 en cifras que hasta hace poco parecían exclusivas del segmento profesional.

Rendimiento estimado e IPC

Las cifras preliminares hablan de una subida de IPC en torno al 8% por el rediseño de caché, con mejoras adicionales del 16‑20% en cargas que no son juegos y escalados notables en multihilo. En escenarios MT, varias fuentes señalan hasta un 67% frente a Zen 6, apoyado en más núcleos por CCD, mejor gestión de caché y densidad.

No todo es marketing: el énfasis recae en latencias, ancho de banda y sostenibilidad de picos. En términos prácticos, esto podría traducirse en tiempos de respuesta más estables en creación de contenido, compilación, simulación y analítica.

Portátiles y consolas portátiles: Grimlock Point y Halo

En movilidad, las APUs Grimlock Point y Grimlock Halo mezclarían núcleos Zen 7 y Zen 7c (y un bloque “Low‑Power”), repitiendo la fórmula de generaciones recientes. Se barajan configuraciones de 4 Zen 7 + 8 Zen 7c (Point) y 8 Zen 7 + 12 Zen 7c (Halo).

La eficiencia sería protagonista: mejoras de rendimiento por vatio de hasta un 36% a 3 W, 32% a 7 W, 25% a 12 W y 17% a 22 W. Esto impactaría directamente en equipos ultraligeros y handhelds, con menos caídas de frames y perfiles térmicos más amables.

Fabricación y calendario

Para los CCD, Zen 7 apuntaría al nodo TSMC A14, una evolución avanzada que reemplaza la nomenclatura clásica de “2 nm”. El encaje industrial sugiere un aterrizaje que, según producto, podría ir de finales de 2027 en movilidad a 2028 en sobremesa y centro de datos.

Este ritmo va en línea con una cadencia de lanzamientos bienal y con la madurez de los nodos de vanguardia, algo que se deja notar también en el coste de fabricación y en la complejidad de integrar más memoria cerca del cómputo.

Plataforma, ISA y funciones de IA

Varias fuentes señalan la posible compatibilidad con AM5, una decisión que, de confirmarse, facilitaría la adopción en el canal retail europeo. A nivel de instrucciones, se espera un nuevo set ISA con soporte de cuantización y mejoras en preparación de datos para aceleradores.

Además, AMD ya ha mencionado oficialmente Zen 7 en su hoja de ruta, anticipando un motor matricial y formatos de datos de IA más amplios integrados en los núcleos. El enfoque va más allá de AVX‑512: la meta es acelerar inferencia y pre/post‑procesado dentro de la CPU generalista.

Servidores y escalado profesional

En el ámbito EPYC, la arquitectura Grimlock buscaría escalar en núcleos y caché manteniendo la filosofía de chiplets. Se priorizarían latencias consistentes y un acceso a L3 más amplio, claves para cargas analíticas y de bases de datos en centros de datos europeos.

Aunque los números exactos cambian según filtración, la dirección es nítida: más densidad por CCD, V‑Cache más grande y caminos internos refinados para sostener tráfico de datos intensivo.

Si los planes se alinean, Zen 7 llegará consolidando el modelo “cache‑first” de AMD: CCD de 16 núcleos, L2 duplicada, V‑Cache con esteroides y un empuje claro en IA y eficiencia. Para usuarios de España y Europa, la hipotética continuidad de AM5 y el foco en rendimiento por vatio ponen a Grimlock en el radar de actualizaciones razonadas, sin alardes, pero con mimbres técnicos de calado.

Soy un apasionado de la tecnología que ha convertido sus intereses «frikis» en profesión. Llevo más de 10 años de mi vida utilizando tecnología de vanguardia y trasteando todo tipo de programas por pura curiosidad. Ahora me he especializado en tecnología de ordenador y videojuegos. Esto es por que desde hace más de 5 años que trabajo redactando para varias webs en materia de tecnología y videojuegos, creando artículos que buscan darte la información que necesitas con un lenguaje entendible por todos.

Si tienes cualquier pregunta, mis conocimientos van desde todo lo relacionado con el sistema operativo Windows así como Android para móviles. Y es que mi compromiso es contigo, siempre estoy dispuesto a dedicarte unos minutos y ayudarte a resolver cualquier duda que tengas en este mundo de internet.